Pencacah Counter Modulo (MOD)

Pencacah (counter) modulo atau hanya MOD adalah pencacah cascaded rangkaian yang menghitung ke nilai modulus yang ditetapkan sebelum mengatur ulang.

Tugas pencacah atau counter adalah menghitung dengan memajukan isi pencacah dengan satu pencacahan dengan setiap pulsa clock. Pencacah yang memajukan urutan angka atau status saat diaktifkan oleh input clock dikatakan beroperasi dalam mode "hitung".

Demikian juga, Pencacah (counter) yang mengurangi urutan angka atau keadaan saat diaktifkan oleh input clock dikatakan beroperasi dalam mode "hitung mundur". Pencacah yang beroperasi dalam mode ATAS dan BAWAH, disebut pencacah dua arah (Counter Bi-directional).

Pencacah (counter) adalah perangkat logika berurutan yang diaktifkan atau dipicu oleh pulsa waktu eksternal atau sinyal clock. Pencacah dapat dibangun untuk beroperasi sebagai Rangkaian Counter Sinkron atau sebagai Rangkaian Counter Asinkron.

Dengan pencacah (counter) Sinkron, semua bit data berubah secara serempak dengan penerapan sinyal clock. Sedangkan rangkaian pencacah (counter) Asinkron tidak tergantung pada clock input sehingga bit data berubah status pada waktu yang berbeda satu demi satu.

Kemudian Pencacah (counter) adalah perangkat logika berurutan yang mengikuti urutan keadaan pencacahan yang ditentukan sebelumnya yang dipicu oleh sinyal clock eksternal (CLK). Jumlah keadaan atau pencacahan urutan melalui mana pencacah tertentu maju sebelum kembali sekali lagi kembali ke keadaan pertama aslinya disebut modulo (MOD).

Dengan kata lain, modulus (atau hanya modulo) adalah jumlah status pencacah yang dihitung dan merupakan jumlah pembagi pencacah. Pencacah (counter) Modulus, atau hanya pencacah MOD, ditentukan berdasarkan jumlah status yang akan dilacak oleh pencacah sebelum kembali ke nilai aslinya.

Sebagai contoh, pencacah (counter) 2-bit yang dihitung dari 002 hingga 112 dalam biner, yaitu 0 hingga 3 dalam desimal, memiliki nilai modulus 4 (00 →1 →10 →11, dan kembali ke 00) Oleh karena itu disebut sebagai counter modulo-4, atau mod-4, counter. Perhatikan juga bahwa diperlukan empat pulsa clock untuk mendapatkan dari 00 hingga 11.

Seperti dalam contoh sederhana ini hanya ada dua bit, (n = 2) maka jumlah maksimum status output yang mungkin (modulus maksimum) untuk pencacah atau counter adalah: 2n = 22 atau 4. Namun, pencacah dapat dirancang untuk menghitung hingga sejumlah keadaan 2n dalam urutannya dengan menyatukan berbagai tahap pencacahan untuk menghasilkan modulo tunggal atau counter MOD-N.

Oleh karena itu, pencacah (counter) "Mod-N" akan membutuhkan "N" jumlah flip-flop yang terhubung bersama untuk menghitung bit data tunggal sambil memberikan 2n status output yang berbeda, (n adalah jumlah bit). Perhatikan bahwa N selalu merupakan nilai integer keseluruhan.

Kita dapat melihat bahwa counter MOD memiliki nilai modulo yang merupakan kekuatan integral dari 2, yaitu, 2, 4, 8, 16 dan seterusnya untuk menghasilkan counter n-bit tergantung pada jumlah flip-flop yang digunakan, dan bagaimana mereka terhubung, menentukan jenis dan modulo dari Pencacah (counter).

Tetapi untuk menjaga hal-hal sederhana, kita akan menggunakan flip-flop tipe-D, (DFF) juga dikenal sebagai Data Latch, karena input data tunggal dan sinyal clock eksternal digunakan, dan juga dipicu tepi positif.

Flip-flop tipe-D, seperti TTL 74LS74, dapat dibuat dari S-R atau J-K based edge-triggered flip-flop yang bergantung pada apakah Anda ingin mengubah status baik pada positif atau tepi terdepan (transisi 0 ke 1) atau pada tepi negatif atau trailing (transisi 1 ke 0) dari pulsa clock.

Di sini kita akan mengasumsikan flip-flop dipicu positif, terdepan. Anda dapat menemukan informasi lebih lanjut di tautan berikut tentang flip-flop tipe-D.

Pengoperasian flip-flop tipe-D (DFF) sangat sederhana karena hanya memiliki input data tunggal, yang disebut "D", dan input clock "CLK" tambahan.

Hal ini memungkinkan bit data tunggal (0 atau 1) disimpan di bawah kendali sinyal clock sehingga menjadikan flip-flop tipe-D perangkat sinkron karena data pada input ditransfer ke output flip-flop hanya pada memicu tepi pulsa clock.

Jadi dari tabel kebenaran, jika ada logika "1" (HIGH) pada input data ketika pulsa clock positif diterapkan, maka flip-flop SET dan menyimpan logika "1" di "Q", dan komplemen " 0” di .

.

Demikian juga, jika ada LOW pada input data ketika clock lain pulsa positif diterapkan, flip-flop RESET dan toko “0” di “Q”, dan menghasilkan “1” di .

.

Kemudian output "Q" dari flip-flop tipe-D menanggapi nilai input "D" ketika input clock (CLK) adalah HIGH. Ketika input clock adalah LOW, kondisi di "Q", "1" atau "0" ditahan sampai waktu berikutnya sinyal clock naik HIGH ke level logika "1".

Oleh karena itu output pada "Q" hanya berubah status ketika input clock berubah dari nilai "0" (LOW) menjadi "1" (HIGH) menjadikannya tepi positif yang dipicu flip-flop tipe-D. Perhatikan bahwa flip-flop negatif yang dipicu tepi bekerja dengan cara yang persis sama, kecuali bahwa tepi jatuh dari pulsa clock adalah tepi pemicu.

Jadi sekarang kita tahu bagaimana flip-flop tipe-D yang dipicu bekerja, mari kita lihat menghubungkan beberapa bersama untuk membentuk Pencacah (counter) MOD.

Dengan menghubungkan output kembali ke input "D" seperti yang ditunjukkan, dan membuat loop umpan balik, kita dapat mengubahnya menjadi pencacah (counter) dibagi dua biner menggunakan input clock hanya karena sinyal output

kembali ke input "D" seperti yang ditunjukkan, dan membuat loop umpan balik, kita dapat mengubahnya menjadi pencacah (counter) dibagi dua biner menggunakan input clock hanya karena sinyal output  selalu kebalikan dari sinyal output Q.

selalu kebalikan dari sinyal output Q.

Diagram waktu menunjukkan bahwa gelombang output "Q" memiliki frekuensi tepat setengah dari input clock, sehingga flip-flop bertindak sebagai pembagi frekuensi.

Jika kita menambahkan flip-flop tipe-D lainnya sehingga output pada "Q" adalah input ke DFF kedua, maka sinyal output dari DFF kedua ini akan menjadi seperempat dari frekuensi input clock, dan seterusnya. Jadi untuk jumlah "n" flip-flop, frekuensi output dibagi dengan 2n, dalam langkah 2.

Perhatikan bahwa metode pembagian frekuensi ini sangat berguna untuk digunakan dalam rangkaian pencacahan berurutan. Misalnya, sinyal frekuensi listrik 60Hz dapat direduksi menjadi sinyal timing 1Hz dengan menggunakan pencacah (counter) divide-by-60.

Pencacah (counter) divide-by-6 akan membagi 60Hz ke 10Hz yang kemudian diumpankan ke counter divide-by-10 untuk membagi 10Hz ke sinyal waktu atau pulsa 1Hz, dll.

Tetapi kita dapat membangun pencacah (counter) MOD untuk menghitung ke nilai apa pun yang kita inginkan dengan menggunakan satu atau lebih gerbang logika eksternal yang menyebabkannya melompati beberapa status output dan berakhir pada pencacahan apa pun yang mengatur ulang pencacah kembali ke nol, semua flip-flop memiliki Q = 0.

Dalam kasus pencacah (counter) modulo "m", mereka tidak menghitung semua status yang mungkin, tetapi menghitung ke nilai "m" dan kemudian kembali ke nol. Jelas, "m" adalah angka yang lebih kecil dari 2n, ( m <2n). Jadi bagaimana kita mendapatkan pencacah (counter) biner untuk kembali ke bagian nol melalui pencacahannya.

Untungnya, selain menghitung, naik atau turun, pencacah juga dapat memiliki input tambahan yang disebut CLEAR dan PRESET yang memungkinkan untuk menghapus pencacahan ke nol, (semua Q = 0) atau untuk menyetel pencacah ke beberapa nilai awal. TTL 74LS74 memiliki input Preset dan Clear yang aktif-rendah.

Mari kita asumsikan untuk kesederhanaan bahwa input CLEAR semuanya terhubung bersamaan dan merupakan input aktif-tinggi yang memungkinkan flip-flop beroperasi secara normal ketika input Clear sama dengan 0 (LOW).

Tetapi jika input Clear berada pada level logika "1" (HIGH), maka tepi positif berikutnya dari sinyal clock akan mengatur ulang semua flip-flop ke status Q = 0, terlepas dari nilai sinyal clock berikutnya.

Perhatikan juga bahwa karena semua input Clear dihubungkan bersama, satu pulsa juga dapat digunakan untuk menghapus output (Q) dari semua flip-flop ke nol sebelum pencacahan dimulai untuk memastikan bahwa pencacahan benar-benar dimulai dari nol.

Juga beberapa pencacah (counter) bit yang lebih besar memiliki pin input ENABLE atau INHIBIT tambahan yang memungkinkan pencacah untuk menghentikan pencacahan pada titik mana pun dalam siklus pencacahan dan mempertahankan statusnya sekarang, sebelum diizinkan untuk melanjutkan pencacahan lagi. Ini berarti pencacah dapat dihentikan dan mulai sesuka hati tanpa mengatur ulang output ke nol.

Tetapi satu flip-flop sendiri menghasilkan urutan pencacahan yang terbatas, jadi dengan menyambungkan lebih banyak flip-flop untuk membentuk rantai, kita dapat meningkatkan kapasitas pencacahan dan membangun pencacah (counter) MOD dari nilai apa pun.

Jika flip-flop tunggal dapat dianggap sebagai pencacah (counter) modulo-2 atau MOD-2, maka menambahkan flip-flop kedua akan memberi kita pencacah (counter) MOD-4 yang memungkinkannya menghitung dalam empat langkah terpisah.

Efek keseluruhan akan membagi sinyal input clock asli dengan empat. Maka urutan biner untuk pencacah (counter) MOD-4 2-bit ini adalah: 00, 01, 10, dan 11 seperti yang ditunjukkan.

Perhatikan bahwa untuk kesederhanaan, transisi switching QA, QB dan CLK dalam diagram waktu di atas ditunjukkan secara simultan meskipun koneksi ini merupakan pencacah (counter) Asinkron. Pada kenyataannya akan ada penundaan switching yang sangat kecil antara penerapan sinyal positif going clock (CLK), dan output pada QA dan QB.

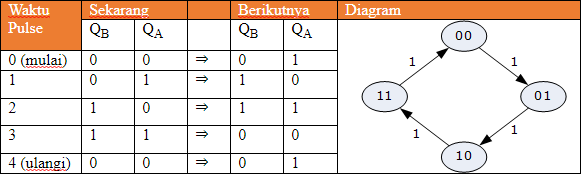

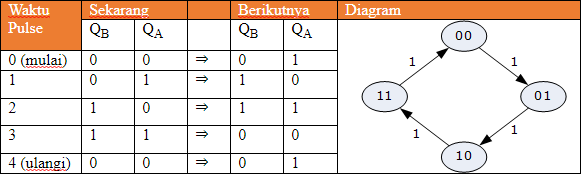

Kami dapat menunjukkan secara visual pengoperasian pencacah (counter) Asinkron 2-bit ini menggunakan tabel kebenaran dan diagram keadaan.

Kita dapat melihat dari tabel kebenaran pencacah, dan dengan membaca nilai-nilai QA dan QB, ketika QA = 0 dan QB = 0, hitungannya adalah 00. Setelah penerapan clock pulse, nilainya menjadi QA = 1, QB = 0, memberikan hitungan 01 dan setelah clock pulsa berikutnya, nilainya menjadi QA = 0, QB = 1, memberikan hitungan 10.

Akhirnya nilai menjadi QA = 1, QB = 1, memberikan hitungan 11 penerapan pulsa clock berikutnya menyebabkan hitungan kembali ke 00, dan setelah itu menghitung terus menerus dalam urutan biner: 00, 01, 10, 11, 00, 01 ... dst.

Kemudian kita telah melihat bahwa pencacah (counter) MOD-2 terdiri dari flip-flop tunggal dan pencacah (counter) MOD-4 membutuhkan dua flip-flop, yang memungkinkannya untuk menghitung dalam empat langkah terpisah.

Kita dapat dengan mudah menambahkan flip-flop lain ke ujung pencacah (counter) MOD-4 untuk menghasilkan pencacah (counter) MOD-8 memberi kita 23 urutan biner pencacahan dari 000 hingga 111, sebelum mengatur ulang ke 000.

Flip-flop keempat akan membuat pencacah (counter) MOD-16 dan seterusnya, pada kenyataannya kita bisa terus menambahkan flip-flop ekstra selama yang kita inginkan.

Mengambil pencacah (counter) MOD-8 di atas, tabel kebenaran untuk hitungan alami diberikan sebagai:

Oleh karena itu kita dapat membangun pencacah (counter) MOD untuk memiliki pencacahan alami 2n menyatakan memberikan pencacah dengan jumlah MOD 2, 4, 8, 16, dan seterusnya, sebelum mengulangi sendiri.

Tetapi kadang-kadang perlu untuk memiliki pencacah (counter) modulo yang me-reset hitungan kembali ke nol selama proses pencacahan normal dan tidak memiliki modulo yang merupakan kekuatan 2. Misalnya, pencacah memiliki modulo 3, 5, 6, atau 10.

Tugas pencacah atau counter adalah menghitung dengan memajukan isi pencacah dengan satu pencacahan dengan setiap pulsa clock. Pencacah yang memajukan urutan angka atau status saat diaktifkan oleh input clock dikatakan beroperasi dalam mode "hitung".

Demikian juga, Pencacah (counter) yang mengurangi urutan angka atau keadaan saat diaktifkan oleh input clock dikatakan beroperasi dalam mode "hitung mundur". Pencacah yang beroperasi dalam mode ATAS dan BAWAH, disebut pencacah dua arah (Counter Bi-directional).

Pencacah (counter) adalah perangkat logika berurutan yang diaktifkan atau dipicu oleh pulsa waktu eksternal atau sinyal clock. Pencacah dapat dibangun untuk beroperasi sebagai Rangkaian Counter Sinkron atau sebagai Rangkaian Counter Asinkron.

Dengan pencacah (counter) Sinkron, semua bit data berubah secara serempak dengan penerapan sinyal clock. Sedangkan rangkaian pencacah (counter) Asinkron tidak tergantung pada clock input sehingga bit data berubah status pada waktu yang berbeda satu demi satu.

Kemudian Pencacah (counter) adalah perangkat logika berurutan yang mengikuti urutan keadaan pencacahan yang ditentukan sebelumnya yang dipicu oleh sinyal clock eksternal (CLK). Jumlah keadaan atau pencacahan urutan melalui mana pencacah tertentu maju sebelum kembali sekali lagi kembali ke keadaan pertama aslinya disebut modulo (MOD).

Dengan kata lain, modulus (atau hanya modulo) adalah jumlah status pencacah yang dihitung dan merupakan jumlah pembagi pencacah. Pencacah (counter) Modulus, atau hanya pencacah MOD, ditentukan berdasarkan jumlah status yang akan dilacak oleh pencacah sebelum kembali ke nilai aslinya.

Sebagai contoh, pencacah (counter) 2-bit yang dihitung dari 002 hingga 112 dalam biner, yaitu 0 hingga 3 dalam desimal, memiliki nilai modulus 4 (00 →1 →10 →11, dan kembali ke 00) Oleh karena itu disebut sebagai counter modulo-4, atau mod-4, counter. Perhatikan juga bahwa diperlukan empat pulsa clock untuk mendapatkan dari 00 hingga 11.

Seperti dalam contoh sederhana ini hanya ada dua bit, (n = 2) maka jumlah maksimum status output yang mungkin (modulus maksimum) untuk pencacah atau counter adalah: 2n = 22 atau 4. Namun, pencacah dapat dirancang untuk menghitung hingga sejumlah keadaan 2n dalam urutannya dengan menyatukan berbagai tahap pencacahan untuk menghasilkan modulo tunggal atau counter MOD-N.

Oleh karena itu, pencacah (counter) "Mod-N" akan membutuhkan "N" jumlah flip-flop yang terhubung bersama untuk menghitung bit data tunggal sambil memberikan 2n status output yang berbeda, (n adalah jumlah bit). Perhatikan bahwa N selalu merupakan nilai integer keseluruhan.

Kita dapat melihat bahwa counter MOD memiliki nilai modulo yang merupakan kekuatan integral dari 2, yaitu, 2, 4, 8, 16 dan seterusnya untuk menghasilkan counter n-bit tergantung pada jumlah flip-flop yang digunakan, dan bagaimana mereka terhubung, menentukan jenis dan modulo dari Pencacah (counter).

Flip-flop tipe D

Pencacah (counter) MOD dibuat menggunakan "flip-flop" dan satu flip-flop dapat menghasilkan hitungan 0 atau 1, memberikan jumlah maksimum 2. Ada berbagai jenis desain flip-flop yang bisa kita gunakan, SR flip-flop, JK flip-flop Master-slave, atau bahkan flip-flop tipe-D untuk membangun pencacah (counter).Tetapi untuk menjaga hal-hal sederhana, kita akan menggunakan flip-flop tipe-D, (DFF) juga dikenal sebagai Data Latch, karena input data tunggal dan sinyal clock eksternal digunakan, dan juga dipicu tepi positif.

Flip-flop tipe-D, seperti TTL 74LS74, dapat dibuat dari S-R atau J-K based edge-triggered flip-flop yang bergantung pada apakah Anda ingin mengubah status baik pada positif atau tepi terdepan (transisi 0 ke 1) atau pada tepi negatif atau trailing (transisi 1 ke 0) dari pulsa clock.

Di sini kita akan mengasumsikan flip-flop dipicu positif, terdepan. Anda dapat menemukan informasi lebih lanjut di tautan berikut tentang flip-flop tipe-D.

Flip-flop tipe-D dan Tabel Kebenaran

Pengoperasian flip-flop tipe-D (DFF) sangat sederhana karena hanya memiliki input data tunggal, yang disebut "D", dan input clock "CLK" tambahan.

Hal ini memungkinkan bit data tunggal (0 atau 1) disimpan di bawah kendali sinyal clock sehingga menjadikan flip-flop tipe-D perangkat sinkron karena data pada input ditransfer ke output flip-flop hanya pada memicu tepi pulsa clock.

Jadi dari tabel kebenaran, jika ada logika "1" (HIGH) pada input data ketika pulsa clock positif diterapkan, maka flip-flop SET dan menyimpan logika "1" di "Q", dan komplemen " 0” di

.

. Demikian juga, jika ada LOW pada input data ketika clock lain pulsa positif diterapkan, flip-flop RESET dan toko “0” di “Q”, dan menghasilkan “1” di

.

.Kemudian output "Q" dari flip-flop tipe-D menanggapi nilai input "D" ketika input clock (CLK) adalah HIGH. Ketika input clock adalah LOW, kondisi di "Q", "1" atau "0" ditahan sampai waktu berikutnya sinyal clock naik HIGH ke level logika "1".

Oleh karena itu output pada "Q" hanya berubah status ketika input clock berubah dari nilai "0" (LOW) menjadi "1" (HIGH) menjadikannya tepi positif yang dipicu flip-flop tipe-D. Perhatikan bahwa flip-flop negatif yang dipicu tepi bekerja dengan cara yang persis sama, kecuali bahwa tepi jatuh dari pulsa clock adalah tepi pemicu.

Jadi sekarang kita tahu bagaimana flip-flop tipe-D yang dipicu bekerja, mari kita lihat menghubungkan beberapa bersama untuk membentuk Pencacah (counter) MOD.

Pencacah (counter) Divide-by-2

Flip-flop tipe-dipicu tepi (edge-triggered) adalah blok bangunan yang berguna dan serbaguna untuk membangun pencacah (counter) MOD atau jenis lain dari rangkaian logika berurutan.Dengan menghubungkan output

kembali ke input "D" seperti yang ditunjukkan, dan membuat loop umpan balik, kita dapat mengubahnya menjadi pencacah (counter) dibagi dua biner menggunakan input clock hanya karena sinyal output

kembali ke input "D" seperti yang ditunjukkan, dan membuat loop umpan balik, kita dapat mengubahnya menjadi pencacah (counter) dibagi dua biner menggunakan input clock hanya karena sinyal output  selalu kebalikan dari sinyal output Q.

selalu kebalikan dari sinyal output Q.Pencacah Counter Divide-by-2 dan Timing Diagram

Diagram waktu menunjukkan bahwa gelombang output "Q" memiliki frekuensi tepat setengah dari input clock, sehingga flip-flop bertindak sebagai pembagi frekuensi.

Jika kita menambahkan flip-flop tipe-D lainnya sehingga output pada "Q" adalah input ke DFF kedua, maka sinyal output dari DFF kedua ini akan menjadi seperempat dari frekuensi input clock, dan seterusnya. Jadi untuk jumlah "n" flip-flop, frekuensi output dibagi dengan 2n, dalam langkah 2.

Perhatikan bahwa metode pembagian frekuensi ini sangat berguna untuk digunakan dalam rangkaian pencacahan berurutan. Misalnya, sinyal frekuensi listrik 60Hz dapat direduksi menjadi sinyal timing 1Hz dengan menggunakan pencacah (counter) divide-by-60.

Pencacah (counter) divide-by-6 akan membagi 60Hz ke 10Hz yang kemudian diumpankan ke counter divide-by-10 untuk membagi 10Hz ke sinyal waktu atau pulsa 1Hz, dll.

Pencacah (counter) Modulo "m"

Pencacah, baik proses Sinkron atau Asinkron satu hitungan pada satu waktu dalam perkembangan biner yang ditetapkan dan sebagai hasilnya, counter bit "n" berfungsi secara alami sebagai pencacah (counter) modulo 2n.Tetapi kita dapat membangun pencacah (counter) MOD untuk menghitung ke nilai apa pun yang kita inginkan dengan menggunakan satu atau lebih gerbang logika eksternal yang menyebabkannya melompati beberapa status output dan berakhir pada pencacahan apa pun yang mengatur ulang pencacah kembali ke nol, semua flip-flop memiliki Q = 0.

Dalam kasus pencacah (counter) modulo "m", mereka tidak menghitung semua status yang mungkin, tetapi menghitung ke nilai "m" dan kemudian kembali ke nol. Jelas, "m" adalah angka yang lebih kecil dari 2n, ( m <2n). Jadi bagaimana kita mendapatkan pencacah (counter) biner untuk kembali ke bagian nol melalui pencacahannya.

Untungnya, selain menghitung, naik atau turun, pencacah juga dapat memiliki input tambahan yang disebut CLEAR dan PRESET yang memungkinkan untuk menghapus pencacahan ke nol, (semua Q = 0) atau untuk menyetel pencacah ke beberapa nilai awal. TTL 74LS74 memiliki input Preset dan Clear yang aktif-rendah.

Mari kita asumsikan untuk kesederhanaan bahwa input CLEAR semuanya terhubung bersamaan dan merupakan input aktif-tinggi yang memungkinkan flip-flop beroperasi secara normal ketika input Clear sama dengan 0 (LOW).

Tetapi jika input Clear berada pada level logika "1" (HIGH), maka tepi positif berikutnya dari sinyal clock akan mengatur ulang semua flip-flop ke status Q = 0, terlepas dari nilai sinyal clock berikutnya.

Perhatikan juga bahwa karena semua input Clear dihubungkan bersama, satu pulsa juga dapat digunakan untuk menghapus output (Q) dari semua flip-flop ke nol sebelum pencacahan dimulai untuk memastikan bahwa pencacahan benar-benar dimulai dari nol.

Juga beberapa pencacah (counter) bit yang lebih besar memiliki pin input ENABLE atau INHIBIT tambahan yang memungkinkan pencacah untuk menghentikan pencacahan pada titik mana pun dalam siklus pencacahan dan mempertahankan statusnya sekarang, sebelum diizinkan untuk melanjutkan pencacahan lagi. Ini berarti pencacah dapat dihentikan dan mulai sesuka hati tanpa mengatur ulang output ke nol.

Pencacah (counter) MOD-4

Secara teknis dan juga sebagai perangkat penyimpanan 1-bit, flip-flop tunggal dapat dianggap sebagai pencacah (counter) MOD-2, karena memiliki output tunggal yang menghasilkan hitungan dua, baik 0 atau 1, pada aplikasi sinyal clock.Tetapi satu flip-flop sendiri menghasilkan urutan pencacahan yang terbatas, jadi dengan menyambungkan lebih banyak flip-flop untuk membentuk rantai, kita dapat meningkatkan kapasitas pencacahan dan membangun pencacah (counter) MOD dari nilai apa pun.

Jika flip-flop tunggal dapat dianggap sebagai pencacah (counter) modulo-2 atau MOD-2, maka menambahkan flip-flop kedua akan memberi kita pencacah (counter) MOD-4 yang memungkinkannya menghitung dalam empat langkah terpisah.

Efek keseluruhan akan membagi sinyal input clock asli dengan empat. Maka urutan biner untuk pencacah (counter) MOD-4 2-bit ini adalah: 00, 01, 10, dan 11 seperti yang ditunjukkan.

Pencacah Counter MOD-4 dan Timing Diagram

Perhatikan bahwa untuk kesederhanaan, transisi switching QA, QB dan CLK dalam diagram waktu di atas ditunjukkan secara simultan meskipun koneksi ini merupakan pencacah (counter) Asinkron. Pada kenyataannya akan ada penundaan switching yang sangat kecil antara penerapan sinyal positif going clock (CLK), dan output pada QA dan QB.

Kami dapat menunjukkan secara visual pengoperasian pencacah (counter) Asinkron 2-bit ini menggunakan tabel kebenaran dan diagram keadaan.

Diagram Keadaan dan Pencacah Counter MOD-4

Kita dapat melihat dari tabel kebenaran pencacah, dan dengan membaca nilai-nilai QA dan QB, ketika QA = 0 dan QB = 0, hitungannya adalah 00. Setelah penerapan clock pulse, nilainya menjadi QA = 1, QB = 0, memberikan hitungan 01 dan setelah clock pulsa berikutnya, nilainya menjadi QA = 0, QB = 1, memberikan hitungan 10.

Akhirnya nilai menjadi QA = 1, QB = 1, memberikan hitungan 11 penerapan pulsa clock berikutnya menyebabkan hitungan kembali ke 00, dan setelah itu menghitung terus menerus dalam urutan biner: 00, 01, 10, 11, 00, 01 ... dst.

Kemudian kita telah melihat bahwa pencacah (counter) MOD-2 terdiri dari flip-flop tunggal dan pencacah (counter) MOD-4 membutuhkan dua flip-flop, yang memungkinkannya untuk menghitung dalam empat langkah terpisah.

Kita dapat dengan mudah menambahkan flip-flop lain ke ujung pencacah (counter) MOD-4 untuk menghasilkan pencacah (counter) MOD-8 memberi kita 23 urutan biner pencacahan dari 000 hingga 111, sebelum mengatur ulang ke 000.

Flip-flop keempat akan membuat pencacah (counter) MOD-16 dan seterusnya, pada kenyataannya kita bisa terus menambahkan flip-flop ekstra selama yang kita inginkan.

Pencacah (counter) Modulo-5

Misalkan kita ingin merancang pencacah (counter) MOD-5, bagaimana kita bisa melakukan itu. Pertama kita tahu bahwa "m = 5", jadi 2n harus lebih besar dari 5. Karena 21 = 2, 22 = 4, 23 = 8, dan 8 lebih besar dari 5, maka kita memerlukan pencacah (counter) dengan tiga flip -flops (N = 3) memberi kita hitungan alami 000 hingga 111 dalam biner (0 hingga 7 desimal).Mengambil pencacah (counter) MOD-8 di atas, tabel kebenaran untuk hitungan alami diberikan sebagai:

Pencacahan Counter MOD-5 dan Tabel Kebenaran

Kemudian kita dapat menggunakan rangkaian decoding logika kombinasional di sekitar pencacah (counter) dasar, baik Sinkron atau Asinkron untuk menghasilkan segala jenis pencacah (counter) MOD yang kita perlukan karena masing-masing keadaan bagian output unik dapat didekodekan untuk mengatur ulang counter pada pencacahan yang diinginkan.

Dalam contoh sederhana kami di atas, kami telah menggunakan 3-input gerbang AND untuk memecahkan kode keadaan 011, tapi pertama kali bahwa QA dan QB keduanya pada logika 1 adalah ketika hitungan mencapai enam, sehingga 2-input gerbang AND terhubung untuk QA dan QB dapat digunakan tanpa komplikasi dari input ketiga dan inverter.

Namun, salah satu kelemahan menggunakan pencacah (counter) Asinkron untuk menghasilkan pencacah (counter) MOD dari pencacahan yang diinginkan adalah bahwa efek yang tidak diinginkan yang disebut "gangguan" dapat terjadi ketika pencacah atau counter mencapai kondisi reset-nya.

Selama waktu yang singkat ini, output pencacah dapat mengambil nilai yang salah, sehingga terkadang lebih baik menggunakan pencacah (counter) Sinkron sebagai pencacah (counter) modulo-m karena semua flip-flop di-clock oleh sinyal clock yang sama sehingga ubah status pada waktu yang sama.

Diagram Keadaan dan Pencacah Counter MOD-8

Oleh karena itu kita dapat membangun pencacah (counter) MOD untuk memiliki pencacahan alami 2n menyatakan memberikan pencacah dengan jumlah MOD 2, 4, 8, 16, dan seterusnya, sebelum mengulangi sendiri.

Tetapi kadang-kadang perlu untuk memiliki pencacah (counter) modulo yang me-reset hitungan kembali ke nol selama proses pencacahan normal dan tidak memiliki modulo yang merupakan kekuatan 2. Misalnya, pencacah memiliki modulo 3, 5, 6, atau 10.

Pencacah Counter MOD-8 dan Tabel Kebenaran

Saat kita membangun pencacah (counter) MOD-5, kita ingin pencacah itu mereset kembali ke nol setelah hitungan 5. Namun, kita dapat melihat dari tabel kebenaran terlampir bahwa hitungan enam memberi kita kondisi output dari: QA = 0, QB = 1, dan QC = 1.

Kita dapat mendekodekan keadaan output ini dari 011 (6) untuk memberi kita sinyal untuk menghapus (Clr) pencacah kembali ke nol dengan bantuan 3-input gerbang AND (TTL 74LS11) dan inverter atau gerbang NOT, (TTL 74LS04 ).

Input dari rangkaian logika kombinasional dari Gerbang NOT (inverter) dan gerbang AND masing-masing terhubung ke QA, QB, dan QC dengan output gerbang AND pada level logika “0” (LOW) untuk setiap kombinasi input selain dari yang kita ingin.

Dalam kode biner, jumlah urutan output akan terlihat seperti ini: 000, 001, 010, 011, 100, 101. Tetapi ketika mencapai keadaan 011 (6), rangkaian logika kombinasional akan mendeteksi keadaan 011 ini dan menghasilkan output pada level logika "1" (HIGH).

Kita kemudian dapat menggunakan output HIGH yang dihasilkan dari gerbang AND untuk mengatur ulang pencacah (counter) kembali ke nol setelah hasilnya 5 (desimal) menghitung memberi kita pencacah (counter) MOD-5 yang diperlukan. Ketika output dari rangkaian kombinasional adalah LOW itu tidak berpengaruh pada urutan pencacahan.

Pencacah (counter) Modulo 10

Contoh yang baik dari rangkaian pencacah (counter) modulo-m yang menggunakan rangkaian kombinasional eksternal untuk menghasilkan pencacah dengan modulo 10 adalah pencacah Decade.

Pencacah (counter) decade (divide-by-10) seperti TTL 74LS90, memiliki 10 status dalam urutan pencacahannya sehingga cocok untuk antarmuka manusia di mana tampilan digital diperlukan.

Counter decade memiliki empat output menghasilkan angka biner 4-bit dan dengan menggunakan Gerbang AND dan Gerbang OR eksternal kita dapat mendeteksi terjadinya status pencacahan ke-9 untuk mengatur ulang pencacah kembali ke nol. Seperti pencacah (counter) mod lainnya, ia menerima pulsa input clock, satu per satu, dan menghitung dari 0 hingga 9 berulang kali.

Setelah mencapai hitungan 9 (1001 dalam biner), counter kembali ke 0000 alih-alih melanjutkan ke 1010. Rangkaian dasar counter satu decade dapat dibuat dari JK flip-flop (TTL 74LS73) yang mengubah status negatif trailing-edge sinyal clock seperti yang ditunjukkan.

Rangkaian Pencacah Counter Decade MOD-10

Ringkasan Pencacah Counter MOD

Kita telah melihat dalam tutorial ini tentang Pencacah (counter) MOD bahwa pencacah atau counter biner adalah rangkaian sekuensial yang menghasilkan urutan bit biner sebagai hasil dari sinyal clock dan keadaan counter biner ditentukan oleh kombinasi spesifik yang dibentuk oleh semua output pencacah bersama-sama.

Jumlah status output yang berbeda yang dapat dihasilkan pencacah disebut counter modulo atau pencacah modulus. Modulus (atau MOD-number) dari pencacah (counter) adalah jumlah total keadaan unik yang dilewatinya dalam satu siklus pencacahan lengkap dengan pencacah (counter) mod-n yang digambarkan juga sebagai counter divide-by-n.

Modulo dari pencacah (counter) diberikan sebagai: 2n di mana n = jumlah flip-flop. Jadi pencacah (counter) 3 flip-flop akan memiliki jumlah maksimum 23= 8 status pencacahan dan akan disebut Pencacah (counter) MOD-8.

Angka biner maksimum yang dapat dihitung oleh Pencacah (counter) adalah 2n –1 yang memberikan jumlah maksimum (111)2 = 23 –1 = 710. Kemudian pencacah dihitung dari 0 hingga 7.

Pencacah (counter) MOD umum termasuk yang dengan nomor MOD 2, 4, 8 dan 16 dan dengan penggunaan rangkaian kombinasional eksternal dapat dikonfigurasi untuk menghitung ke nilai yang telah ditentukan selain dari satu dengan modulo 2n maksimum. Secara umum, pengaturan apa pun dari sejumlah "m" flip-flop dapat digunakan untuk membangun pencacah (counter) MOD apa pun.

Modulo umum untuk pencacah dengan urutan terpotong adalah sepuluh (1010), yang disebut MOD-10. Pencacah (counter) dengan sepuluh keadaan bagian dalam urutannya dikenal sebagai pencacah (counter) decade.

Pencacah (counter) decade berguna untuk antarmuka ke tampilan digital. Pencacah (counter) MOD lainnya termasuk pencacah (counter) MOD-6 atau MOD-12 yang memiliki aplikasi dalam clock digital untuk menampilkan waktu hari.