Pencacah (Counter) Asinkron

Pencacah (counter) Asinkron menggunakan flip-flop yang dihubungkan secara seri sehingga pulsa clock input nampak beriak melalui pencacah (counter). Sebuah pencacah Asinkron dapat memiliki 2n-1 mungkin keadaan pencacahan misalnya MOD-16 untuk counter 4-bit, (0-15) sehingga ideal untuk digunakan dalam aplikasi Pembagi Frekuensi.

Tetapi juga dimungkinkan untuk menggunakan konfigurasi pencacah asinkron dasar untuk membangun pencacah khusus dengan status pencacahan kurang dari jumlah output maksimumnya. Misalnya, modulo atau pencacah (counter) MOD. Ini dicapai dengan memaksa pencacah untuk mengatur ulang sendiri ke nol pada nilai yang ditentukan sebelumnya menghasilkan jenis pencacah asinkron yang memiliki urutan terpotong.

Kemudian pencacah n-bit yang menghitung hingga modulus maksimumnya (2n) disebut pencacah sekuensial penuh dan pencacah n-bit yang modulusnya lebih kecil dari kemungkinan maksimum disebut pencacah terpotong.

Tetapi mengapa kita ingin membuat pencacah (counter) terpotong asinkron yang bukan MOD-4, MOD-8, atau modulo lain yang sama dengan kekuatan dua. Jawabannya adalah kita dapat menggunakan logika kombinasional untuk mengambil keuntungan dari input asinkron pada flip-flop.

Jika kita mengambil pencacah (counter) asinkron modulo-16 dan memodifikasinya dengan gerbang logika tambahan, dapat dibuat untuk menghasilkan keluaran pencacah dekade (bagi-oleh-10) untuk digunakan dalam pencacah-an desimal standar dan rangkaian aritmatika.

Pencacah seperti itu umumnya disebut sebagai Pencacah Counter Decade. Pencacah (counter) dekade membutuhkan pengaturan ulang ke nol ketika jumlah output mencapai nilai desimal 10, yaitu. ketika DCBA = 1010 dan untuk melakukan ini kita perlu memasukkan kondisi ini kembali ke input reset.

Pencacah dengan urutan hitungan dari biner "0000" (BCD = "0") hingga "1001" (BCD = "9") umumnya disebut sebagai pencacah desimal berkode-biner BCD karena urutan sepuluh statusnya adalah bahwa dari kode BCD tetapi pencacah dekade biner lebih umum.

Jenis pencacah (counter) asinkron ini dihitung ke atas pada setiap tepi trailing sinyal clock input mulai dari 0000 hingga mencapai output 1001 (desimal 9). Kedua output QA dan QD sekarang sama dengan logika "1".

Pada aplikasi pulsa clock berikutnya, output dari gerbang NAND 74LS10 mengubah status dari logika “1” ke level logika “0”. Gerbang NAND 74LS10 mengubah status dari logika “1” ke level logika “0”. Karena output dari gerbang NAND terhubung ke input CLEAR ( ) dari semua Flip Flops 74LS73, sinyal ini menyebabkan semua output Q diatur ulang ke binary 0000 pada hitungan 10.

) dari semua Flip Flops 74LS73, sinyal ini menyebabkan semua output Q diatur ulang ke binary 0000 pada hitungan 10.

Sebagai output QA dan QD sekarang sama dengan logika "0" karena flip-flop baru saja direset, output dari gerbang NAND kembali ke level logika "1" dan pencacah (counter) memulai kembali dari 0000. Kami sekarang memiliki dekade atau Modulo-10 up-counter.

Dengan menggunakan ide yang sama untuk memotong urutan output counter, rangkaian di atas dapat dengan mudah disesuaikan dengan siklus pencacah-an lainnya dengan hanya mengubah koneksi ke input gerbang NAND atau dengan menggunakan kombinasi gerbang logika lainnya.

Jadi misalnya, skala dua belas (modulo-12) dapat dengan mudah dibuat dengan hanya mengambil input ke gerbang NAND dari output di " QC " dan " QD ", mencatat bahwa biner setara dengan 12 adalah 1100 dan bahwa output "QA" adalah bit kurang signifikan (LSB).

Karena modulo maksimum yang dapat diimplementasikan dengan n flip-flop adalah 2n, ini berarti bahwa ketika Anda merancang pencacah (counter) asinkron terpotong, Anda harus menentukan daya terendah dua yang lebih besar dari atau sama dengan modulo yang Anda inginkan.

Katakanlah kita ingin menghitung dari 0 hingga 39, atau mod-40 dan ulangi. Maka jumlah flip-flop tertinggi yang dibutuhkan adalah enam, n = 6 memberikan MOD maksimum 64 karena lima flip-flop tidak akan cukup karena ini hanya memberi kita MOD-32.

Sekarang anggaplah kita ingin membangun pencacah (counter) "divide-by-128" untuk pembagian frekuensi, kita perlu membuat tujuh flip-flop dari 128 = 27. Menggunakan dual flip-flop seperti 74LS74 kita masih membutuhkan empat IC untuk menyelesaikan rangkaian.

Salah satu metode alternatif yang mudah adalah dengan menggunakan dua TTL 7493 sebagai pencacah/pembagi riak 4-bit. Karena 128 = 16 x 8, satu 7493 dapat dikonfigurasikan sebagai pencacah "divide-by-16" dan yang lainnya sebagai pencacah "divide-by-8". Kedua IC tersebut akan di-cascade bersama untuk membentuk pembagi frekuensi “divide-by-128” seperti yang ditunjukkan.

Salah satu metode alternatif yang mudah adalah dengan menggunakan dua TTL 7493 sebagai pencacah/pembagi riak 4-bit. Karena 128 = 16 x 8, satu 7493 dapat dikonfigurasikan sebagai pencacah "divide-by-16" dan yang lainnya sebagai pencacah "divide-by-8". Kedua IC tersebut akan di-cascade bersama untuk membentuk pembagi frekuensi “divide-by-128” seperti yang ditunjukkan.

Tentu saja pencacah (counter) asinkron IC standar tersedia seperti pencacah/pembagi riak yang dapat diprogram TTL 74LS90 yang dapat dikonfigurasikan sebagai divide-by-2, divide-by-5 atau kombinasi keduanya. 74LS390 adalah IC dua decade driver yang sangat fleksibel dengan sejumlah besar kombinasi "divide-by" tersedia mulai dari divide-by-2, 4, 5, 10, 20, 25, 50, dan 100.

Kita dapat dengan mudah menghasilkan sinyal gelombang persegi 1Hz menggunakan chip timer 555 standar yang dikonfigurasikan sebagai Multivibrator Astabil, tetapi lembar data pabrikan memberi tahu kami bahwa timer 555 memiliki kesalahan waktu tipikal 1-2% tergantung pada produsen, dan pada tingkat rendah frekuensi 1Hz, kesalahan waktu 2% ini tidak baik.

Namun, lembar data juga memberi tahu kita bahwa frekuensi operasi maksimum dari timer 555 adalah sekitar 300kHz dan kesalahan 2% pada frekuensi tinggi ini, sementara masih besar pada sekitar 6kHz maksimum, akan dapat diterima. Jadi dengan memilih frekuensi timing yang lebih tinggi, katakanlah 262.144kHz dan pencacah (counter) riak 18-bit (Modulo-18), kita dapat dengan mudah membuat sinyal timing 1Hz presisi seperti yang ditunjukkan di bawah ini.

Ini tentu saja merupakan contoh yang sangat sederhana tentang bagaimana menghasilkan frekuensi waktu yang akurat, tetapi dengan menggunakan osilator kristal frekuensi tinggi dan pembagi frekuensi multi-bit, generator frekuensi presisi dapat dihasilkan untuk berbagai aplikasi mulai dari clock atau arloji hingga waktu acara dan bahkan aplikasi piano/synthesizer atau jenis musik elektronik.

Sayangnya salah satu kelemahan utama dengan pencacah (counter) asinkron adalah bahwa ada sedikit keterlambatan antara kedatangan pulsa clock pada inputnya dan hadir pada outputnya karena rangkaian internal gerbang.

Dalam rangkaian asinkron, keterlambatan ini disebut Propagasi Delay yang memberikan pencacah riak asinkron julukan "propagasi counter" dan dalam beberapa kasus frekuensi tinggi, keterlambatan ini dapat menghasilkan jumlah output yang salah.

Dalam rangkaian pencacah (counter) riak bit besar, jika penundaan tahapan yang terpisah ditambahkan bersama untuk memberikan penundaan yang dijumlahkan pada akhir rantai pencacah (counter), perbedaan waktu antara sinyal input dan sinyal output yang dihitung bisa sangat besar. Inilah sebabnya mengapa pencacah (counter) Asinkron umumnya tidak digunakan dalam rangkaian pencacah-an frekuensi tinggi jika sejumlah besar bit terlibat.

Juga, output dari pencacah (counter) tidak memiliki hubungan waktu tetap satu sama lain dan tidak terjadi pada saat yang bersamaan karena urutan pencatatan clock kerja. Dengan kata lain frekuensi output menjadi tersedia satu per satu, semacam efek domino.

Kemudian, semakin banyak flip-flop yang ditambahkan ke rantai pencacah asinkron, semakin rendah frekuensi operasi maksimum untuk memastikan pencacah-an yang akurat. Untuk mengatasi masalah keterlambatan propagasi, Pencacah Counter Sinkron dikembangkan.

Kemudian untuk merangkum beberapa KELEBIHAN dari Pencacah (counter) Asinkron:

Tetapi juga dimungkinkan untuk menggunakan konfigurasi pencacah asinkron dasar untuk membangun pencacah khusus dengan status pencacahan kurang dari jumlah output maksimumnya. Misalnya, modulo atau pencacah (counter) MOD. Ini dicapai dengan memaksa pencacah untuk mengatur ulang sendiri ke nol pada nilai yang ditentukan sebelumnya menghasilkan jenis pencacah asinkron yang memiliki urutan terpotong.

Kemudian pencacah n-bit yang menghitung hingga modulus maksimumnya (2n) disebut pencacah sekuensial penuh dan pencacah n-bit yang modulusnya lebih kecil dari kemungkinan maksimum disebut pencacah terpotong.

Tetapi mengapa kita ingin membuat pencacah (counter) terpotong asinkron yang bukan MOD-4, MOD-8, atau modulo lain yang sama dengan kekuatan dua. Jawabannya adalah kita dapat menggunakan logika kombinasional untuk mengambil keuntungan dari input asinkron pada flip-flop.

Jika kita mengambil pencacah (counter) asinkron modulo-16 dan memodifikasinya dengan gerbang logika tambahan, dapat dibuat untuk menghasilkan keluaran pencacah dekade (bagi-oleh-10) untuk digunakan dalam pencacah-an desimal standar dan rangkaian aritmatika.

Pencacah seperti itu umumnya disebut sebagai Pencacah Counter Decade. Pencacah (counter) dekade membutuhkan pengaturan ulang ke nol ketika jumlah output mencapai nilai desimal 10, yaitu. ketika DCBA = 1010 dan untuk melakukan ini kita perlu memasukkan kondisi ini kembali ke input reset.

Pencacah dengan urutan hitungan dari biner "0000" (BCD = "0") hingga "1001" (BCD = "9") umumnya disebut sebagai pencacah desimal berkode-biner BCD karena urutan sepuluh statusnya adalah bahwa dari kode BCD tetapi pencacah dekade biner lebih umum.

Pencacah (counter) Dekade Asinkron

Jenis pencacah (counter) asinkron ini dihitung ke atas pada setiap tepi trailing sinyal clock input mulai dari 0000 hingga mencapai output 1001 (desimal 9). Kedua output QA dan QD sekarang sama dengan logika "1".

Pada aplikasi pulsa clock berikutnya, output dari gerbang NAND 74LS10 mengubah status dari logika “1” ke level logika “0”. Gerbang NAND 74LS10 mengubah status dari logika “1” ke level logika “0”. Karena output dari gerbang NAND terhubung ke input CLEAR (

) dari semua Flip Flops 74LS73, sinyal ini menyebabkan semua output Q diatur ulang ke binary 0000 pada hitungan 10.

) dari semua Flip Flops 74LS73, sinyal ini menyebabkan semua output Q diatur ulang ke binary 0000 pada hitungan 10.Sebagai output QA dan QD sekarang sama dengan logika "0" karena flip-flop baru saja direset, output dari gerbang NAND kembali ke level logika "1" dan pencacah (counter) memulai kembali dari 0000. Kami sekarang memiliki dekade atau Modulo-10 up-counter.

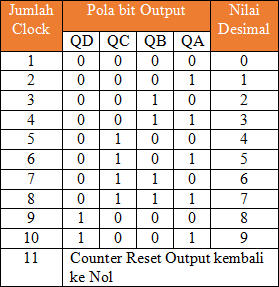

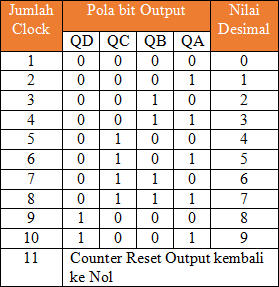

Tabel Kebenaran Counter Decade

Timing Diagram Pencacah Counter Decade

Dengan menggunakan ide yang sama untuk memotong urutan output counter, rangkaian di atas dapat dengan mudah disesuaikan dengan siklus pencacah-an lainnya dengan hanya mengubah koneksi ke input gerbang NAND atau dengan menggunakan kombinasi gerbang logika lainnya.

Jadi misalnya, skala dua belas (modulo-12) dapat dengan mudah dibuat dengan hanya mengambil input ke gerbang NAND dari output di " QC " dan " QD ", mencatat bahwa biner setara dengan 12 adalah 1100 dan bahwa output "QA" adalah bit kurang signifikan (LSB).

Karena modulo maksimum yang dapat diimplementasikan dengan n flip-flop adalah 2n, ini berarti bahwa ketika Anda merancang pencacah (counter) asinkron terpotong, Anda harus menentukan daya terendah dua yang lebih besar dari atau sama dengan modulo yang Anda inginkan.

Katakanlah kita ingin menghitung dari 0 hingga 39, atau mod-40 dan ulangi. Maka jumlah flip-flop tertinggi yang dibutuhkan adalah enam, n = 6 memberikan MOD maksimum 64 karena lima flip-flop tidak akan cukup karena ini hanya memberi kita MOD-32.

Sekarang anggaplah kita ingin membangun pencacah (counter) "divide-by-128" untuk pembagian frekuensi, kita perlu membuat tujuh flip-flop dari 128 = 27. Menggunakan dual flip-flop seperti 74LS74 kita masih membutuhkan empat IC untuk menyelesaikan rangkaian.

Tentu saja pencacah (counter) asinkron IC standar tersedia seperti pencacah/pembagi riak yang dapat diprogram TTL 74LS90 yang dapat dikonfigurasikan sebagai divide-by-2, divide-by-5 atau kombinasi keduanya. 74LS390 adalah IC dua decade driver yang sangat fleksibel dengan sejumlah besar kombinasi "divide-by" tersedia mulai dari divide-by-2, 4, 5, 10, 20, 25, 50, dan 100.

Pembagi Frekuensi

Kemampuan pencacah (counter) riak untuk memotong urutan untuk menghasilkan output "divide-by-n" berarti bahwa pencacah dan terutama pencacah riak, dapat digunakan sebagai pembagi frekuensi untuk mengurangi frekuensi clock tinggi ke nilai yang lebih bermanfaat untuk digunakan dalam digital clock dan aplikasi waktu. Sebagai contoh, anggap kita memerlukan sinyal timing 1Hz yang akurat untuk mengoperasikan clock digital.Kita dapat dengan mudah menghasilkan sinyal gelombang persegi 1Hz menggunakan chip timer 555 standar yang dikonfigurasikan sebagai Multivibrator Astabil, tetapi lembar data pabrikan memberi tahu kami bahwa timer 555 memiliki kesalahan waktu tipikal 1-2% tergantung pada produsen, dan pada tingkat rendah frekuensi 1Hz, kesalahan waktu 2% ini tidak baik.

Namun, lembar data juga memberi tahu kita bahwa frekuensi operasi maksimum dari timer 555 adalah sekitar 300kHz dan kesalahan 2% pada frekuensi tinggi ini, sementara masih besar pada sekitar 6kHz maksimum, akan dapat diterima. Jadi dengan memilih frekuensi timing yang lebih tinggi, katakanlah 262.144kHz dan pencacah (counter) riak 18-bit (Modulo-18), kita dapat dengan mudah membuat sinyal timing 1Hz presisi seperti yang ditunjukkan di bawah ini.

Sinyal Timing 1Hz dari Pencacah (counter) Riak Asinkron 18-bit

Ini tentu saja merupakan contoh yang sangat sederhana tentang bagaimana menghasilkan frekuensi waktu yang akurat, tetapi dengan menggunakan osilator kristal frekuensi tinggi dan pembagi frekuensi multi-bit, generator frekuensi presisi dapat dihasilkan untuk berbagai aplikasi mulai dari clock atau arloji hingga waktu acara dan bahkan aplikasi piano/synthesizer atau jenis musik elektronik.

Sayangnya salah satu kelemahan utama dengan pencacah (counter) asinkron adalah bahwa ada sedikit keterlambatan antara kedatangan pulsa clock pada inputnya dan hadir pada outputnya karena rangkaian internal gerbang.

Dalam rangkaian asinkron, keterlambatan ini disebut Propagasi Delay yang memberikan pencacah riak asinkron julukan "propagasi counter" dan dalam beberapa kasus frekuensi tinggi, keterlambatan ini dapat menghasilkan jumlah output yang salah.

Dalam rangkaian pencacah (counter) riak bit besar, jika penundaan tahapan yang terpisah ditambahkan bersama untuk memberikan penundaan yang dijumlahkan pada akhir rantai pencacah (counter), perbedaan waktu antara sinyal input dan sinyal output yang dihitung bisa sangat besar. Inilah sebabnya mengapa pencacah (counter) Asinkron umumnya tidak digunakan dalam rangkaian pencacah-an frekuensi tinggi jika sejumlah besar bit terlibat.

Juga, output dari pencacah (counter) tidak memiliki hubungan waktu tetap satu sama lain dan tidak terjadi pada saat yang bersamaan karena urutan pencatatan clock kerja. Dengan kata lain frekuensi output menjadi tersedia satu per satu, semacam efek domino.

Kemudian, semakin banyak flip-flop yang ditambahkan ke rantai pencacah asinkron, semakin rendah frekuensi operasi maksimum untuk memastikan pencacah-an yang akurat. Untuk mengatasi masalah keterlambatan propagasi, Pencacah Counter Sinkron dikembangkan.

Kemudian untuk merangkum beberapa KELEBIHAN dari Pencacah (counter) Asinkron:

- Pencacah Asinkron dapat dengan mudah dibuat dari Toggle atau flip-flop tipe-D.

- Mereka disebut "pencacah Asinkron" karena input clock dari flip-flop tidak semuanya digerakkan oleh sinyal clock yang sama.

- Setiap output dalam rantai tergantung pada perubahan status dari output flip-flop sebelumnya.

- Pencacah asinkron kadang-kadang disebut pencacah riak karena data muncul untuk "riak" dari output satu flip-flop ke input berikutnya.

- Mereka dapat diimplementasikan menggunakan rangkaian pencacah (counter) "divide-by-n".

- Pencacah terpotong dapat menghasilkan jumlah nomor modulo.

- Flip-flop output "sinkronisasi ulang" tambahan mungkin diperlukan.

- Untuk menghitung urutan terpotong tidak sama dengan 2n, logika umpan balik tambahan diperlukan.

- Menghitung sejumlah besar bit, keterlambatan propagasi secara bertahap dapat menjadi besar yang tidak diinginkan.

- Penundaan ini memberi mereka julukan "Counter Propagation".

- Kesalahan pencacah-an terjadi pada frekuensi clocking tinggi.

- Counter Synchronous atau Pencacah Sinkron lebih cepat dan lebih dapat diandalkan karena mereka menggunakan sinyal clock yang sama untuk semua flip-flop.