I2C (Inter-Integrated Circuit) Penerjemah Tingkat Tegangan untuk Komunikasi Serial

I2C (Inter-Integrated Circuit) adalah standar serial bus dua kawat multi-master untuk multi-slave yang memungkinkan...

I2C (Inter-Integrated Circuit) adalah standar bus serial dua-kawat multi-master hingga multi-slave yang memungkinkan komunikasi serial pada sejumlah bit rate (tergantung mode yang didukung) melalui beberapa meter kabel. I2C adalah standar yang relatif lama, tetapi masih sangat populer yang tiba di tempat kejadian pada tahun 1982.

Sejak itu, antarmuka logika 5V telah memberikan jalan ke standar tegangan yang jauh lebih rendah dan sistem bus I2C perlu mengakomodasi untuk pemindahan level untuk memungkinkan komunikasi dengan perangkat tegangan antarmuka yang berbeda pada bus yang sama. Kecepatan data komunikasi juga meningkat dari kecepatan clock 100 kHz asli hingga 5MHz dalam mode ultra-cepat, dan level shifting harus mampu mengakomodasi laju data yang lebih tinggi ini.

Sinyal I2C terdiri dari sinyal data tunggal yang membawa level logika divalidasi oleh sinyal clock. Kedua sinyal dua arah, digerakkan oleh satu atau lebih master atau slave tergantung pada kondisi sistem. Untuk mencegah pertikaian yang merusak yang disebabkan oleh output yang mendorong satu sama lain, Drain terbuka atau output Collector terbuka dengan resistor pull up menggerakkan bus.

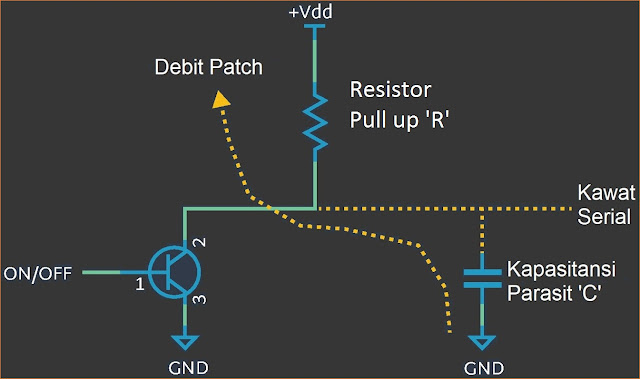

Output open drain (berbasis FET) atau open collector (berbasis BJT) adalah output yang tidak memiliki gerbang aktif yang mengarah ke supply positif. Mematikan gerbang output menempatkan output dalam keadaan impedansi tinggi. Kawat sinyal mengapung tinggi karena muatan yang disimpan oleh kapasitansi bus terlepas melalui resistansi tarikan seperti yang ditunjukkan pada Gambar 1.

Oleh karena itu, kecepatan transisi antara rendah ke tinggi pada sinyal bus dibatasi oleh waktu yang diperlukan untuk muatan listrik yang disimpan pada kapasitansi parasit pada kawat 'C' untuk dikeluarkan melalui resistansi pull-up 'R', 3dB. titik yang didefinisikan oleh persamaan: f3dB = 1/(2π.RC)

Misalnya, jika pemuatan bus kapasitif gabungan adalah 100pF, dan resistansi pull-up gabungan pada sinyal di bus menjadi 1.5kΩ, titik 3dB sekitar 1MHz. Ini membatasi kecepatan data maksimum yang mungkin di bus tetapi memiliki manfaat yang jelas karena tidak pernah memiliki situasi di mana output impedansi rendah saling mendorong, menyebabkan arus tinggi yang merusak mengalir melalui gerbang. Sifat dua arah dari sinyal I2C , variasi level tegangan bus dan persyaratan output drain terbuka sangat menyulitkan rangkaian terjemahan level.

I2C secara umum telah memenuhi standar logika 5V, tetapi berpotensi perlu bekerja dengan banyak standar antarmuka tegangan rendah lainnya. Bahkan ketika ambang antarmuka standar dan daerah tampak dalam rentang yang dapat diterima, margin kebisingan mengurangi kinerja bus tanpa terjemahan tingkat logika yang tepat.

Sistem bus harus kompatibel dengan kombinasi tingkat logika kasus terburuk terkait dengan masing-masing perangkat pada variasi perangkat dan kisaran suhu yang diantisipasi. Perhatikan bahwa setiap perangkat di bus umum meningkatkan kapasitansi dan selanjutnya dapat mengurangi margin. Bus berujung tunggal, terutama yang memiliki kabel panjang, mengalami impedansi di ground atau supply yang menyebabkan ring edge dan ground bouncing - efek yang semakin mengurangi margin level.

Penggunaan buffer dua arah mungkin tidak secara spesifik menawarkan terjemahan tegangan yang berbeda, tetapi dapat membantu mempertahankan toleransi tegangan di mana level sinyal kompatibel di antara standar. I2C Repeater juga menyediakan cara untuk mengisolasi muatan kapasitif bus dengan membaginya menjadi dua, memperluas jalur kabel atau sejumlah perangkat yang dapat didukung dalam suatu sistem.

Antarmuka I2C sangat toleran terhadap kabel yang panjang karena kecepatan data yang rendah, dukungan pensinyalan 5V dan sifat drain terbuka. Karakteristik ini membuatnya digunakan dalam situasi di mana perangkat yang terpasang dan keluar dari bus serial menambah kompleksitas rangkaian terjemahan level dan koneksi yang terbuka menambah persyaratan untuk perlindungan pelepasan muatan listrik statis (ESD).

Antarmuka I2C memiliki going edge positif yang dibatasi oleh efek ini. Rangkaian MOSFET memperkenalkan kapasitansi parasit tambahan (misalnya efek Miller) dan tingkat peralihan yang selanjutnya mendistorsi karakteristik kedua sisi selama perubahan arah. Ini dapat menyebabkan masalah jika antarmuka logika marginal karena mereka memiliki wilayah transisi di sekitar ambang batas di mana output tidak pasti.

Sinyal yang berada di dalam rentang ini menyebabkan apa yang disebut 'status meta-stabil' yang menyebabkan gangguan sinyal. Input pemicu Schmitt adalah antarmuka khusus dengan Histerisis tegangan yang disebabkan oleh umpan balik positif dari output gerbang input. Ini meningkatkan margin noise dan mengurangi potensi metastabilitas karena sinyal yang berubah dengan lambat.

Selain itu, sinyal noise, lambat atau non-monotonik, dapat ada pada I2C serial bus juga diperbaiki menggunakan algoritma debounce. Algoritma debounce memperkenalkan waktu tunggu di mana sinyal input dipantau selama periode waktu untuk level sinyal kontinu sebelum berubah, menolak transisi kesalahan yang termasuk dalam periode ini. Ini adalah teknik yang digunakan dengan FPGA dan implementasi perangkat lunak 'bit-banging' pada mikrokontroler.

Metode umum untuk mengisolasi secara elektrik bus I2C juga menggabungkan terjemahan level sebagai batas isolasi dan memungkinkan dukungan tegangan pada kedua sisi batas isolasi. Teknik isolasi konvensional meliputi isolasi fotovoltaik melalui optocoupler atau perangkat yang memodulasi informasi sinyal bus serial melintasi jembatan kapasitif atau transformator induktif.

Opto-listrik isolasi I2C-bus, seperti rangkaian yang dijelaskan pada Gambar 5, mampu beroperasi pada kecepatan lebih dari 1Mbps. Catatan aplikasi NXP AN10364 adalah deskripsi komprehensif dari berbagai topologi untuk antarmuka antara perangkat I2C dengan berbagai potensi dan tegangan ground lokal. Topologi serupa ditemukan dalam aplikasi yang membutuhkan komunikasi sisi primer ke sekunder di rangkaian daya listrik AC terisolasi, peralatan medis, dan Power of Ethernet (PoE).

Perangkat tersebut sangat baik untuk mendukung koneksi I2C dari periferal slave 5V dan 3V3 ke bank I/O tegangan rendah dari FPGA atau mikrokontroler. Perangkat penerjemah tingkat tegangan dua arah drain terbuka ganda seperti NVT2001 menyederhanakan arsitektur bus multi-tegangan karena jumlah komponen yang rendah, fleksibilitas solusi yang tinggi, perlindungan ESD terintegrasi dan paket fisik kecil.

I2C (Inter-Integrated Circuit) adalah standar bus serial dua-kawat multi-master hingga multi-slave yang memungkinkan komunikasi serial pada sejumlah bit rate (tergantung mode yang didukung) melalui beberapa meter kabel. I2C adalah standar yang relatif lama, tetapi masih sangat populer yang tiba di tempat kejadian pada tahun 1982.

Sejak itu, antarmuka logika 5V telah memberikan jalan ke standar tegangan yang jauh lebih rendah dan sistem bus I2C perlu mengakomodasi untuk pemindahan level untuk memungkinkan komunikasi dengan perangkat tegangan antarmuka yang berbeda pada bus yang sama. Kecepatan data komunikasi juga meningkat dari kecepatan clock 100 kHz asli hingga 5MHz dalam mode ultra-cepat, dan level shifting harus mampu mengakomodasi laju data yang lebih tinggi ini.

Sinyal I2C terdiri dari sinyal data tunggal yang membawa level logika divalidasi oleh sinyal clock. Kedua sinyal dua arah, digerakkan oleh satu atau lebih master atau slave tergantung pada kondisi sistem. Untuk mencegah pertikaian yang merusak yang disebabkan oleh output yang mendorong satu sama lain, Drain terbuka atau output Collector terbuka dengan resistor pull up menggerakkan bus.

| |

|

Oleh karena itu, kecepatan transisi antara rendah ke tinggi pada sinyal bus dibatasi oleh waktu yang diperlukan untuk muatan listrik yang disimpan pada kapasitansi parasit pada kawat 'C' untuk dikeluarkan melalui resistansi pull-up 'R', 3dB. titik yang didefinisikan oleh persamaan: f3dB = 1/(2π.RC)

Misalnya, jika pemuatan bus kapasitif gabungan adalah 100pF, dan resistansi pull-up gabungan pada sinyal di bus menjadi 1.5kΩ, titik 3dB sekitar 1MHz. Ini membatasi kecepatan data maksimum yang mungkin di bus tetapi memiliki manfaat yang jelas karena tidak pernah memiliki situasi di mana output impedansi rendah saling mendorong, menyebabkan arus tinggi yang merusak mengalir melalui gerbang. Sifat dua arah dari sinyal I2C , variasi level tegangan bus dan persyaratan output drain terbuka sangat menyulitkan rangkaian terjemahan level.

Kompatibilitas Tingkat Logika

Level atau tingkat logika yang berbeda memiliki tegangan ambang logika yang berbeda yang menentukan transisi logika tinggi/rendah. Standar tegangan yang berbeda juga menyebabkan masalah karena adanya sambungan Dioda pada input dan output Perangkat Semikonduktor. Level sinyal yang didorong lebih tinggi dari tegangan supply memaksa dioda ke konduksi dalam kondisi destruktif yang disebut "latch-up".I2C secara umum telah memenuhi standar logika 5V, tetapi berpotensi perlu bekerja dengan banyak standar antarmuka tegangan rendah lainnya. Bahkan ketika ambang antarmuka standar dan daerah tampak dalam rentang yang dapat diterima, margin kebisingan mengurangi kinerja bus tanpa terjemahan tingkat logika yang tepat.

| |

|

Penggunaan buffer dua arah mungkin tidak secara spesifik menawarkan terjemahan tegangan yang berbeda, tetapi dapat membantu mempertahankan toleransi tegangan di mana level sinyal kompatibel di antara standar. I2C Repeater juga menyediakan cara untuk mengisolasi muatan kapasitif bus dengan membaginya menjadi dua, memperluas jalur kabel atau sejumlah perangkat yang dapat didukung dalam suatu sistem.

Antarmuka I2C sangat toleran terhadap kabel yang panjang karena kecepatan data yang rendah, dukungan pensinyalan 5V dan sifat drain terbuka. Karakteristik ini membuatnya digunakan dalam situasi di mana perangkat yang terpasang dan keluar dari bus serial menambah kompleksitas rangkaian terjemahan level dan koneksi yang terbuka menambah persyaratan untuk perlindungan pelepasan muatan listrik statis (ESD).

Metode Tingkat Terjemahan MOSFET diskrit

Pergeseran tingkat dua arah harus dilakukan di kedua arah. Metode paling sederhana menggunakan MOSFET seperti yang digambarkan pada gambar 3, dan dijelaskan secara lebih rinci dalam catatan aplikasi AN10441. Meskipun level pergeseran MOSFET dapat diterima untuk standar komunikasi 100kHz hingga 400kHz, itu tidak memiliki kinerja yang diperlukan untuk mode operasi yang lebih cepat karena keterbatasan frekuensi yang disebutkan sebelumnya yang dipaksakan oleh konstanta waktu RC. Dalam kasus di mana mode bandwidth yang lebih tinggi digunakan, perangkat penerjemah tingkat tujuan khusus diperlukan. |

| Gambar 3: Terjemahan Tingkat Berbasis MOSFET |

Sinyal yang berada di dalam rentang ini menyebabkan apa yang disebut 'status meta-stabil' yang menyebabkan gangguan sinyal. Input pemicu Schmitt adalah antarmuka khusus dengan Histerisis tegangan yang disebabkan oleh umpan balik positif dari output gerbang input. Ini meningkatkan margin noise dan mengurangi potensi metastabilitas karena sinyal yang berubah dengan lambat.

Selain itu, sinyal noise, lambat atau non-monotonik, dapat ada pada I2C serial bus juga diperbaiki menggunakan algoritma debounce. Algoritma debounce memperkenalkan waktu tunggu di mana sinyal input dipantau selama periode waktu untuk level sinyal kontinu sebelum berubah, menolak transisi kesalahan yang termasuk dalam periode ini. Ini adalah teknik yang digunakan dengan FPGA dan implementasi perangkat lunak 'bit-banging' pada mikrokontroler.

Metode Terisolasi

Sistem seperti dijelaskan pada gambar 4 adalah sistem non-terisolasi dengan koneksi listrik langsung antara kedua perangkat, terlepas dari terjemahan level tegangan. Karena antarmuka I2C tidak seimbang dan dapat memiliki kabel interkoneksi yang panjang, perbedaan potensial ini dapat menyebabkan arus kebisingan atau noise palsu pada sinyal ground. Lahan yang tidak diisolasi dapat menyebabkan kondisi gangguan yang berbahaya ketika berurusan dengan rangkaian tegangan tinggi. I2C interface yang digunakan dalam aplikasi yang melintasi batas isolasi harus memenuhi standar keselamatan dan membutuhkan isolasi galvanik.

|

Gambar 4: Terjemahan Tingkat Non-Terisolasi

|

Semua ini cenderung untuk berbagi karakteristik umum dari pemisahan/rekombinasi sinyal dua arah menjadi dua jalur searah. Beberapa aplikasi memperpanjang panjang kabel yang didukung dan meningkatkan kekebalan kebisingan dengan mengubah sinyal ke standar diferensial (seperti RS485). Mereka juga dapat menggunakan tegangan pensinyalan yang lebih tinggi.

|

Gambar 5: Multi-drop I2C Terisolasi dengan Level Tegangan Independen

|

Penerjemah Tingkat Tegangan Dua Arah

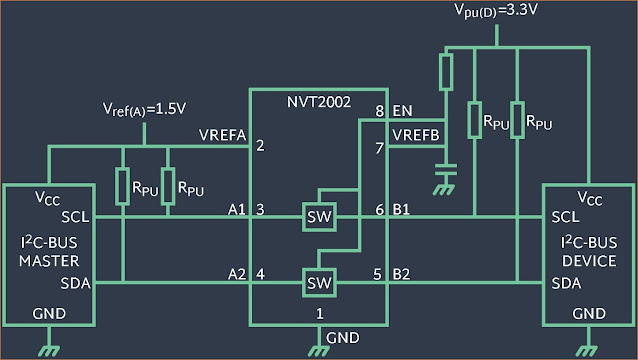

Penerjemah tegangan dua arah dapat bekerja pada bus I2C. Penting untuk memastikan perangkat memiliki orientasi bus yang benar - mencocokkan level tegangan bus ke sisi penerjemah yang benar. Kebanyakan penerjemah akan menentukan satu sisi lebih besar dari tegangan minimum (biasanya sekitar 1V) daripada sisi lainnya. Kedua belah pihak masih akan memerlukan pull-up untuk operasi I2C yang benar seperti yang dijelaskan dalam catatan aplikasi AN11127.

|

Gambar 6: Penerjemah Tingkat Dua Arah di rangkaian I2C

|

Mereka juga berfungsi untuk menyediakan isolasi antara elemen yang lebih lambat dan lebih cepat pada bus I2C, memungkinkan mereka untuk beroperasi dalam desain yang sama. Mengontrol pin yang diaktifkan untuk memutuskan koneksi bus yang lebih lambat selama komunikasi mode cepat menyediakan koeksistensi.

Perangkat ini menampilkan penundaan propagasi kurang dari 1.5ns (tidak termasuk pemuatan bus) dan kinerja clock 33MHz dalam sistem drain terbuka. Dukungan frekuensi tinggi memungkinkan solusi untuk mode operasi ultra-cepat untuk menggabungkan pemindahan level dan meningkatkan kemungkinan standar antarmuka I2C kecepatan yang lebih tinggi di masa depan.

Perangkat ini menampilkan penundaan propagasi kurang dari 1.5ns (tidak termasuk pemuatan bus) dan kinerja clock 33MHz dalam sistem drain terbuka. Dukungan frekuensi tinggi memungkinkan solusi untuk mode operasi ultra-cepat untuk menggabungkan pemindahan level dan meningkatkan kemungkinan standar antarmuka I2C kecepatan yang lebih tinggi di masa depan.