Gerbang Transmisi - Gabungan NMOS dan PMOS

Gerbang transmisi adalah sebuah sakelar bilateral yang terdiri dari transistor NMOS dan PMOS yang dikendalikan oleh level logika yang diterapkan secara eksternal.

Sakelar analog adalah sakelar semikonduktor solid-state yang mengontrol jalur transmisi sinyal analog. Operasi posisi sakelar yang terbuka dan tertutup biasanya dikontrol oleh beberapa jaringan logika digital, dengan sakelar analog standar tersedia dalam banyak gaya dan konfigurasi.

Sebagai contoh, konfigurasi tunggal atau ganda normally open (NO) atau normally closed (NC), single-pole single-throw (SPST), single-pole, double-throw (SPDT) dll, dalam banyak cara yang sama seperti untuk relai elektromekanis konvensional dan kontak.

Peralihan dan perutean sinyal digital dan analog (baik tegangan maupun arus) dapat dengan mudah dilakukan dengan menggunakan relai mekanis dan kontaknya, tetapi ini bisa lambat dan mahal.

Pilihan yang jelas adalah dengan menggunakan sakelar elektronik solid state bertindak jauh lebih cepat yang menggunakan gerbang analog metal oxide semiconductor (MOS) untuk merutekan arus sinyal dari input mereka ke output mereka, dengan sakelar bilateral CMOS 4016B yang terkenal menjadi contoh paling umum.

Teknologi MOS menggunakan perangkat NMOS dan PMOS untuk melakukan fungsi switching logika, sehingga memungkinkan komputer digital atau rangkaian logika untuk mengontrol operasi sakelar analog ini.

Perangkat CMOS tempat transistor NMOS dan PMOS dibuat dalam rangkaian gerbang yang sama, dapat melewati (kondisi tertutup) atau memblokir (kondisi terbuka) sinyal analog atau digital, tergantung pada level logika digital yang mengendalikannya.

Jenis sakelar solid-state yang memungkinkan untuk transfer sinyal atau data di kedua arah disebut Gerbang Transmisi, atau TG. Tetapi pertama-tama mari kita mempertimbangkan operasi Field Effect Transistor, atau Transistor FET sebagai sakelar analog dasar.

Kelebihan utama dari MOSFET, atau FET logam-oksida-semikonduktor, teknologi dibandingkan perangkat bipolar adalah bahwa terminal gerbangnya diisolasi dari saluran konduksi utama oleh lapisan tipis oksida logam, dan saluran MOSFET utama yang digunakan untuk beralih murni resistif.

Pertimbangkan konfigurasi dasar N-channel dan P-channel enhancement MOSFET (eMOSFET) di bawah ini.

Kemudian kita dapat melihat bahwa untuk MOSFET perangkat tambahan n-channel (NMOS) dan p-channel (PMOS) beroperasi sebagai perangkat open (OFF) atau closed (ON), kondisi berikut ini harus benar:

Juga, karena eMOSFET digunakan terutama sebagai perangkat switching, ia umumnya beroperasi antara daerah cut-off dan saturasi sehingga VGS bertindak sebagai tegangan kontrol ON/OFF untuk MOSFET.

Sakelar analog yang ideal akan menciptakan kondisi hubung singkat saat tertutup dan kondisi kran terbuka saat terbuka, dengan cara yang mirip dengan sakelar mekanis.

Namun, sakelar analog solid state tidak ideal karena selalu ada beberapa kelemahan yang terkait dengan saluran penghantar karena terdapat nilai resistifnya ketika AKTIF.

Kami ingin berpikir bahwa jika kita menerapkan sinyal ke pin inputnya, ini akan menghasilkan sinyal yang identik dan tanpa kehilangan pada pin output, dan sebaliknya.

Namun, sementara sakelar CMOS memang membuat gerbang transmisi yang sangat baik, resistansi keadaan "ON", RON dapat berupa beberapa ohm yang menyebabkan hilangnya daya I2*R, sedangkan resistansi keadaan "OFF" dapat beberapa ribu ohm memungkinkan pico ampere arus masih mengalir melalui channel.

Namun demikian, kemampuan FET semikonduktor oksida logam pelengkap untuk bekerja sebagai sakelar analog dan gerbang transmisi tetap tinggi, dan perangkat MOSFET, khususnya perangkat tambahan MOSFET yang memerlukan tegangan untuk diterapkan ke pintu gerbang untuk mengubahnya “ON” dan tegangan nol untuk mengubahnya "OFF" adalah transistor switching yang paling umum digunakan.

Ketika tegangan kontrol, VC pada gerbang adalah nol (RENDAH), terminal gerbang tidak akan positif sehubungan dengan terminal input (drain) atau terminal output (sumber), sehingga transistor berada di daerah cut-off dan terminal input dan output diisolasi dari masing-masing terminal.

Kemudian NMOS bertindak sebagai sakelar terbuka sehingga setiap tegangan pada input tidak akan diteruskan ke output.

Ketika ada kontrol tegangan positif +VC di terminal gerbang, transistor dihidupkan “ON” dan dalam bertindak daerah saturasi sebagai sakelar tertutup.

Jika tegangan input, VIN positif dan lebih besar dari VC arus akan mengalir dari terminal drain ke terminal sumber, sehingga menghubungkan VOUT ke VDI.

Namun jika VIN menjadi nol (RENDAH) sementara tegangan kontrol gerbang masih positif, channel/saluran transistor masih terbuka tetapi tegangan drain-to-source, VDS adalah nol, sehingga tidak ada arus drain yang mengalir melalui saluran dan dengan demikian output tegangannya nol.

Oleh karena itu, selama tegangan kontrol gerbang, VC adalah TINGGI, transistor NMOS meneruskan tegangan input ke output. Jika RENDAH, transistor NMOS dihidupkan "OFF", dan terminal output terputus dari input. Dengan demikian, kontrol tegangan, VC di gerbang menentukan apakah transistor adalah “terbuka” atau “tertutup” sebagai sakelar.

Satu masalah di sini dengan sakelar NMOS adalah bahwa tegangan gerbang-ke-sumber, VGS harus secara signifikan lebih besar dari tegangan ambang batas saluran untuk memutarnya sepenuhnya-ON atau akan ada pengurangan tegangan melalui saluran.

Dengan demikian perangkat NMOS hanya dapat mentransmisikan logika "lemah" "1" (TINGGI) tetapi logika kuat "0" (RENDAH) tanpa kehilangan.

Untuk PMOS FET, ketika tegangan kontrol, VC di gerbang nol dan dengan demikian lebih negatif sehubungan dengan terminal input (sumber) atau terminal output (drain), transistor "ON" dan di daerah saturasinya bertindak sebagai sakelar tertutup.

Jika tegangan input, VIN positif dan lebih besar dari VC arus akan mengalir dari terminal sumber ke terminal drain, yang ID mengalir keluar dari drain sehingga menghubungkan VIN ke VOUT.

Jika tegangan input, VIN menjadi nol (RENDAH) sementara tegangan kontrol gerbang masih nol atau negatif, saluran PMOS masih terbuka tetapi tegangan sumber-ke-drain, VSD adalah nol, sehingga tidak ada arus yang mengalir melalui saluran dan dengan demikian tegangan pada keluaran (drain) adalah nol.

Ketika ada kontrol tegangan positif +VC di terminal gerbang, saluran transistor PMOS diaktifkan “OFF” dan di wilayah akting cut-off sebagai sakelar terbuka. Dengan demikian tidak ada arus yang mengalir, ID mengalir melalui saluran penghantar.

Oleh karena itu, selama tegangan kontrol gerbang, VC adalah RENDAH (atau negatif), transistor PMOS akan melewatkan tegangan input ke output. Jika TINGGI, transistor PMOS dinyalakan "OFF", dan terminal output terputus dari input.

Jadi seperti pada perangkat NMOS sebelumnya, tegangan kontrol, VC di gerbang menentukan apakah transistor adalah "terbuka" atau "ditutup" sebagai sakelar.

Masalah dengan sakelar PMOS adalah bahwa tegangan gerbang-ke-sumber, VGS harus jauh lebih kecil daripada tegangan ambang batas saluran untuk memutarnya sepenuhnya-OFF atau arus masih akan mengalir melalui saluran. Dengan demikian perangkat PMOS dapat mentransmisikan logika "kuat" "1" (TINGGI) tanpa kehilangan tetapi logika lemah "0" (RENDAH).

Jadi kita dapat melihat bahwa untuk perangkat NMOS, tegangan gerbang-ke-sumber positif menyebabkan arus mengalir dalam satu arah dari Drain-to-Source, sedangkan untuk perangkat PMOS, tegangan gerbang-ke-sumber negatif akan mengakibatkan arus mengalir dalam arah sebaliknya dari Source-to-Drain.

Namun, perangkat NMOS hanya melewati "0" yang kuat tetapi "1" lemah, sedangkan perangkat PMOS melewati "1" yang kuat tetapi "0" lemah.

Jadi dengan menggabungkan karakteristik NMOS dan perangkat PMOS, dimungkinkan untuk mentransmisikan baik logika kuat "0" atau nilai logika "1" kuat di kedua arah tanpa degradasi apa pun. Ini kemudian membentuk dasar Gerbang Transmisi.

Perhatikan bahwa gerbang transmisi sangat berbeda dari gerbang logika CMOS konvensional karena gerbang transmisi simetris, atau bilateral, yaitu, input dan output dapat dipertukarkan.

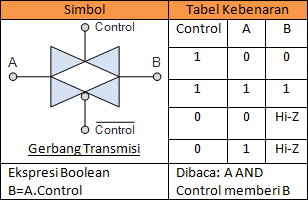

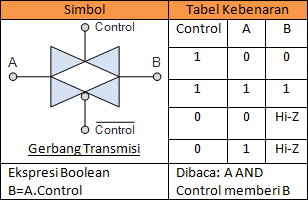

Operasi bilateral ini ditunjukkan pada simbol gerbang transmisi di bawah ini yang menunjukkan dua segitiga bertumpukan yang menunjuk ke arah yang berlawanan untuk menunjukkan dua arah sinyal.

Dua transistor MOS terhubung back-to-back secara paralel dengan inverter yang digunakan antara gerbang NMOS dan PMOS untuk menyediakan dua tegangan kontrol pelengkap.

Ketika sinyal kontrol input, VC adalah RENDAH, baik transistor NMOS dan PMOS terputus dan sakelar terbuka. Ketika VC tinggi, kedua perangkat bias menjadi konduksi dan sakelar ditutup.

Dengan demikian gerbang transmisi bertindak sebagai sakelar “tertutup” ketika VC = 1, sedangkan gerbang bertindak sebagai sakelar “terbuka” ketika VC = 0 beroperasi sebagai sakelar yang dikontrol tegangan. Gelembung simbol yang menunjukkan gerbang FET PMOS.

Kita dapat melihat dari tabel kebenaran di atas, bahwa output pada B tidak hanya bergantung pada level logika input A, tetapi juga pada level logika yang ada pada input kontrol. Dengan demikian nilai level logika B didefinisikan sebagai Kontrol A DAN memberi kita ekspresi boolean untuk gerbang transmisi:

Karena ekspresi boolean dari gerbang transmisi menggabungkan fungsi logika gerbang AND, oleh karena itu dimungkinkan untuk melaksanakan operasi ini menggunakan gerbang AND 2-input standar dengan satu input menjadi input data sementara yang lain adalah input kontrol seperti yang ditunjukkan.

Satu hal lain yang perlu dipertimbangkan tentang gerbang transmisi, NMOS tunggal atau PMOS tunggal dapat digunakan sebagai sakelar CMOS, tetapi kombinasi dari dua transistor secara paralel memiliki beberapa keunggulan. Saluran FET bersifat resistif sehingga resistansi ON dari kedua transistor secara efektif terhubung secara paralel.

Sebagai FET pada-Resistansi adalah fungsi dari tegangan gerbang-ke-sumber, VGS, karena satu transistor menjadi kurang konduktor karena drive gerbang, transistor lain mengambil alih dan menjadi lebih konduktor.

Dengan demikian nilai gabungan dari dua resistansi-ON (serendah 2 atau 3Ω) tetap lebih atau kurang konstan daripada yang akan terjadi pada transistor switching tunggal sendiri. Bisa menunjukkan ini dalam diagram berikut.

Gerbang Transmisi, (TG) adalah sebuah sakelar bilateral di mana salah satu dari terminal dapat menjadi input atau output. Selain terminal input dan output, gerbang transmisi memiliki koneksi ketiga yang disebut kontrol, di mana input kontrol menentukan keadaan switching gerbang sebagai sakelar terbuka atau tertutup (NO/NC).

Input ini biasanya digerakkan oleh sinyal logika digital yang berganti-ganti antara arde (0V) dan tegangan DC, biasanya VDD. Ketika input kontrol rendah (Kontrol = 0), sakelar terbuka, dan ketika input kontrol TINGGI (Kontrol = 1) sakelar ditutup.

Gerbang transmisi bertindak seperti sakelar yang dikendalikan tegangan, dan sebagai sakelar, gerbang transmisi CMOS dapat digunakan untuk mengalihkan baik sinyal analog maupun digital yang melewati rentang tegangan penuh (dari 0V ke VDD) di kedua arah, yang seperti yang dibahas tidak mungkin dilakukan dengan satu perangkat MOS.

Kombinasi dari transistor NMOS dan PMOS bersama-sama dalam gerbang tunggal berarti bahwa transistor NMOS akan mentransfer logika yang baik "0" tetapi logika buruk "1", sedangkan transistor PMOS mentransfer logika yang baik "1" tetapi logika yang buruk "0".

Oleh karena itu, menghubungkan transistor NMOS dengan transistor PMOS secara paralel menghasilkan sakelar bilateral tunggal yang menawarkan kemampuan drive output yang efisien untuk gerbang logika CMOS yang dikendalikan oleh level logika input tunggal.

Sakelar analog adalah sakelar semikonduktor solid-state yang mengontrol jalur transmisi sinyal analog. Operasi posisi sakelar yang terbuka dan tertutup biasanya dikontrol oleh beberapa jaringan logika digital, dengan sakelar analog standar tersedia dalam banyak gaya dan konfigurasi.

Sebagai contoh, konfigurasi tunggal atau ganda normally open (NO) atau normally closed (NC), single-pole single-throw (SPST), single-pole, double-throw (SPDT) dll, dalam banyak cara yang sama seperti untuk relai elektromekanis konvensional dan kontak.

Peralihan dan perutean sinyal digital dan analog (baik tegangan maupun arus) dapat dengan mudah dilakukan dengan menggunakan relai mekanis dan kontaknya, tetapi ini bisa lambat dan mahal.

Pilihan yang jelas adalah dengan menggunakan sakelar elektronik solid state bertindak jauh lebih cepat yang menggunakan gerbang analog metal oxide semiconductor (MOS) untuk merutekan arus sinyal dari input mereka ke output mereka, dengan sakelar bilateral CMOS 4016B yang terkenal menjadi contoh paling umum.

Teknologi MOS menggunakan perangkat NMOS dan PMOS untuk melakukan fungsi switching logika, sehingga memungkinkan komputer digital atau rangkaian logika untuk mengontrol operasi sakelar analog ini.

Perangkat CMOS tempat transistor NMOS dan PMOS dibuat dalam rangkaian gerbang yang sama, dapat melewati (kondisi tertutup) atau memblokir (kondisi terbuka) sinyal analog atau digital, tergantung pada level logika digital yang mengendalikannya.

Jenis sakelar solid-state yang memungkinkan untuk transfer sinyal atau data di kedua arah disebut Gerbang Transmisi, atau TG. Tetapi pertama-tama mari kita mempertimbangkan operasi Field Effect Transistor, atau Transistor FET sebagai sakelar analog dasar.

MOSFET sebagai Sakelar Analog

Transistor Bipolar (BJT) dan Transistor (FET) dapat digunakan sebagai sakelar elektronik kutub tunggal dalam beragam aplikasi yang berbeda.Kelebihan utama dari MOSFET, atau FET logam-oksida-semikonduktor, teknologi dibandingkan perangkat bipolar adalah bahwa terminal gerbangnya diisolasi dari saluran konduksi utama oleh lapisan tipis oksida logam, dan saluran MOSFET utama yang digunakan untuk beralih murni resistif.

Pertimbangkan konfigurasi dasar N-channel dan P-channel enhancement MOSFET (eMOSFET) di bawah ini.

MOSFET sebagai Sakelar

Kemudian kita dapat melihat bahwa untuk MOSFET perangkat tambahan n-channel (NMOS) dan p-channel (PMOS) beroperasi sebagai perangkat open (OFF) atau closed (ON), kondisi berikut ini harus benar:

- N-channel MOSFET berperilaku seperti sakelar tertutup ketika tegangan gerbang-sumber, VGS lebih besar dari tegangan ambang, VT. Itu adalah VGS > VT

- N-channel MOSFET berperilaku seperti sakelar terbuka ketika tegangan gerbang-sumber, VGS kurang dari tegangan ambang, VT. Itu adalah VGS <VT

- P-channel MOSFET berperilaku seperti sakelar tertutup ketika tegangan gerbang-drain, VGD kurang dari tegangan ambang, VT. Itu adalah VGD <VT

- P-channel MOSFET berperilaku seperti sakelar terbuka ketika tegangan gerbang-drain, VGD lebih besar dari tegangan ambang, VT. Itu adalah VGD > VT

Juga, karena eMOSFET digunakan terutama sebagai perangkat switching, ia umumnya beroperasi antara daerah cut-off dan saturasi sehingga VGS bertindak sebagai tegangan kontrol ON/OFF untuk MOSFET.

Sakelar Ideal

Sakelar analog yang ideal akan menciptakan kondisi hubung singkat saat tertutup dan kondisi kran terbuka saat terbuka, dengan cara yang mirip dengan sakelar mekanis.

Namun, sakelar analog solid state tidak ideal karena selalu ada beberapa kelemahan yang terkait dengan saluran penghantar karena terdapat nilai resistifnya ketika AKTIF.

Kami ingin berpikir bahwa jika kita menerapkan sinyal ke pin inputnya, ini akan menghasilkan sinyal yang identik dan tanpa kehilangan pada pin output, dan sebaliknya.

Namun, sementara sakelar CMOS memang membuat gerbang transmisi yang sangat baik, resistansi keadaan "ON", RON dapat berupa beberapa ohm yang menyebabkan hilangnya daya I2*R, sedangkan resistansi keadaan "OFF" dapat beberapa ribu ohm memungkinkan pico ampere arus masih mengalir melalui channel.

Namun demikian, kemampuan FET semikonduktor oksida logam pelengkap untuk bekerja sebagai sakelar analog dan gerbang transmisi tetap tinggi, dan perangkat MOSFET, khususnya perangkat tambahan MOSFET yang memerlukan tegangan untuk diterapkan ke pintu gerbang untuk mengubahnya “ON” dan tegangan nol untuk mengubahnya "OFF" adalah transistor switching yang paling umum digunakan.

Sakelar NMOS

Transistor N-channel metal-oksida semikonduktor (NMOS) dapat digunakan sebagai gerbang transmisi untuk melewati sinyal analog. Dengan asumsi bahwa terminal drain dan sumber identik, input terhubung ke terminal Drain dan sinyal kontrol ke terminal gerbang seperti yang ditunjukkan.NMOS FET sebagai Sakelar Analog

Ketika tegangan kontrol, VC pada gerbang adalah nol (RENDAH), terminal gerbang tidak akan positif sehubungan dengan terminal input (drain) atau terminal output (sumber), sehingga transistor berada di daerah cut-off dan terminal input dan output diisolasi dari masing-masing terminal.

Kemudian NMOS bertindak sebagai sakelar terbuka sehingga setiap tegangan pada input tidak akan diteruskan ke output.

Ketika ada kontrol tegangan positif +VC di terminal gerbang, transistor dihidupkan “ON” dan dalam bertindak daerah saturasi sebagai sakelar tertutup.

Jika tegangan input, VIN positif dan lebih besar dari VC arus akan mengalir dari terminal drain ke terminal sumber, sehingga menghubungkan VOUT ke VDI.

Namun jika VIN menjadi nol (RENDAH) sementara tegangan kontrol gerbang masih positif, channel/saluran transistor masih terbuka tetapi tegangan drain-to-source, VDS adalah nol, sehingga tidak ada arus drain yang mengalir melalui saluran dan dengan demikian output tegangannya nol.

Oleh karena itu, selama tegangan kontrol gerbang, VC adalah TINGGI, transistor NMOS meneruskan tegangan input ke output. Jika RENDAH, transistor NMOS dihidupkan "OFF", dan terminal output terputus dari input. Dengan demikian, kontrol tegangan, VC di gerbang menentukan apakah transistor adalah “terbuka” atau “tertutup” sebagai sakelar.

Satu masalah di sini dengan sakelar NMOS adalah bahwa tegangan gerbang-ke-sumber, VGS harus secara signifikan lebih besar dari tegangan ambang batas saluran untuk memutarnya sepenuhnya-ON atau akan ada pengurangan tegangan melalui saluran.

Dengan demikian perangkat NMOS hanya dapat mentransmisikan logika "lemah" "1" (TINGGI) tetapi logika kuat "0" (RENDAH) tanpa kehilangan.

Sakelar PMOS

Transistor P-channel metal-oksida semikonduktor (PMOS) serupa tetapi berlawanan dalam polaritas dengan perangkat NMOS sebelumnya dengan arus yang mengalir dalam arah yang berlawanan, dari sumber ke saluran. Kemudian untuk perangkat PMOS, input terhubung ke terminal Sumber dan sinyal kontrol ke terminal gerbang seperti yang ditunjukkan.PMOS FET sebagai Sakelar

Untuk PMOS FET, ketika tegangan kontrol, VC di gerbang nol dan dengan demikian lebih negatif sehubungan dengan terminal input (sumber) atau terminal output (drain), transistor "ON" dan di daerah saturasinya bertindak sebagai sakelar tertutup.

Jika tegangan input, VIN positif dan lebih besar dari VC arus akan mengalir dari terminal sumber ke terminal drain, yang ID mengalir keluar dari drain sehingga menghubungkan VIN ke VOUT.

Jika tegangan input, VIN menjadi nol (RENDAH) sementara tegangan kontrol gerbang masih nol atau negatif, saluran PMOS masih terbuka tetapi tegangan sumber-ke-drain, VSD adalah nol, sehingga tidak ada arus yang mengalir melalui saluran dan dengan demikian tegangan pada keluaran (drain) adalah nol.

Ketika ada kontrol tegangan positif +VC di terminal gerbang, saluran transistor PMOS diaktifkan “OFF” dan di wilayah akting cut-off sebagai sakelar terbuka. Dengan demikian tidak ada arus yang mengalir, ID mengalir melalui saluran penghantar.

Oleh karena itu, selama tegangan kontrol gerbang, VC adalah RENDAH (atau negatif), transistor PMOS akan melewatkan tegangan input ke output. Jika TINGGI, transistor PMOS dinyalakan "OFF", dan terminal output terputus dari input.

Jadi seperti pada perangkat NMOS sebelumnya, tegangan kontrol, VC di gerbang menentukan apakah transistor adalah "terbuka" atau "ditutup" sebagai sakelar.

Masalah dengan sakelar PMOS adalah bahwa tegangan gerbang-ke-sumber, VGS harus jauh lebih kecil daripada tegangan ambang batas saluran untuk memutarnya sepenuhnya-OFF atau arus masih akan mengalir melalui saluran. Dengan demikian perangkat PMOS dapat mentransmisikan logika "kuat" "1" (TINGGI) tanpa kehilangan tetapi logika lemah "0" (RENDAH).

Jadi kita dapat melihat bahwa untuk perangkat NMOS, tegangan gerbang-ke-sumber positif menyebabkan arus mengalir dalam satu arah dari Drain-to-Source, sedangkan untuk perangkat PMOS, tegangan gerbang-ke-sumber negatif akan mengakibatkan arus mengalir dalam arah sebaliknya dari Source-to-Drain.

Namun, perangkat NMOS hanya melewati "0" yang kuat tetapi "1" lemah, sedangkan perangkat PMOS melewati "1" yang kuat tetapi "0" lemah.

Jadi dengan menggabungkan karakteristik NMOS dan perangkat PMOS, dimungkinkan untuk mentransmisikan baik logika kuat "0" atau nilai logika "1" kuat di kedua arah tanpa degradasi apa pun. Ini kemudian membentuk dasar Gerbang Transmisi.

Gerbang Transmisi

Menghubungkan perangkat PMOS dan NMOS bersamaan secara paralel, kita dapat membuat sakelar CMOS bilateral dasar, yang umumnya dikenal sebagai "Gerbang Transmisi".Perhatikan bahwa gerbang transmisi sangat berbeda dari gerbang logika CMOS konvensional karena gerbang transmisi simetris, atau bilateral, yaitu, input dan output dapat dipertukarkan.

Operasi bilateral ini ditunjukkan pada simbol gerbang transmisi di bawah ini yang menunjukkan dua segitiga bertumpukan yang menunjuk ke arah yang berlawanan untuk menunjukkan dua arah sinyal.

Gerbang Transmisi CMOS

Dua transistor MOS terhubung back-to-back secara paralel dengan inverter yang digunakan antara gerbang NMOS dan PMOS untuk menyediakan dua tegangan kontrol pelengkap.

Ketika sinyal kontrol input, VC adalah RENDAH, baik transistor NMOS dan PMOS terputus dan sakelar terbuka. Ketika VC tinggi, kedua perangkat bias menjadi konduksi dan sakelar ditutup.

Dengan demikian gerbang transmisi bertindak sebagai sakelar “tertutup” ketika VC = 1, sedangkan gerbang bertindak sebagai sakelar “terbuka” ketika VC = 0 beroperasi sebagai sakelar yang dikontrol tegangan. Gelembung simbol yang menunjukkan gerbang FET PMOS.

Ekspresi Boolean Gerbang Transmisi

Seperti gerbang logika murni, kita dapat mendefinisikan operasi gerbang transmisi menggunakan tabel kebenaran dan ekspresi boolean sebagai berikut.Tabel Kebenaran Gerbang Transmisi

Kita dapat melihat dari tabel kebenaran di atas, bahwa output pada B tidak hanya bergantung pada level logika input A, tetapi juga pada level logika yang ada pada input kontrol. Dengan demikian nilai level logika B didefinisikan sebagai Kontrol A DAN memberi kita ekspresi boolean untuk gerbang transmisi:

B = A.Control

Karena ekspresi boolean dari gerbang transmisi menggabungkan fungsi logika gerbang AND, oleh karena itu dimungkinkan untuk melaksanakan operasi ini menggunakan gerbang AND 2-input standar dengan satu input menjadi input data sementara yang lain adalah input kontrol seperti yang ditunjukkan.

Implementasi Gerbang AND

Satu hal lain yang perlu dipertimbangkan tentang gerbang transmisi, NMOS tunggal atau PMOS tunggal dapat digunakan sebagai sakelar CMOS, tetapi kombinasi dari dua transistor secara paralel memiliki beberapa keunggulan. Saluran FET bersifat resistif sehingga resistansi ON dari kedua transistor secara efektif terhubung secara paralel.

Sebagai FET pada-Resistansi adalah fungsi dari tegangan gerbang-ke-sumber, VGS, karena satu transistor menjadi kurang konduktor karena drive gerbang, transistor lain mengambil alih dan menjadi lebih konduktor.

Dengan demikian nilai gabungan dari dua resistansi-ON (serendah 2 atau 3Ω) tetap lebih atau kurang konstan daripada yang akan terjadi pada transistor switching tunggal sendiri. Bisa menunjukkan ini dalam diagram berikut.

Gerbang Transmisi Resistansi-ON

Ringkasan Gerbang Transmisi

Kita telah melihat di sini bahwa menghubungkan P-channel FET (PMOS) dengan N-channel FET (NMOS) kita dapat membuat sakelar solid-state yang dikontrol secara digital menggunakan tegangan level logika dan umumnya disebut "gerbang transmisi".Gerbang Transmisi, (TG) adalah sebuah sakelar bilateral di mana salah satu dari terminal dapat menjadi input atau output. Selain terminal input dan output, gerbang transmisi memiliki koneksi ketiga yang disebut kontrol, di mana input kontrol menentukan keadaan switching gerbang sebagai sakelar terbuka atau tertutup (NO/NC).

Input ini biasanya digerakkan oleh sinyal logika digital yang berganti-ganti antara arde (0V) dan tegangan DC, biasanya VDD. Ketika input kontrol rendah (Kontrol = 0), sakelar terbuka, dan ketika input kontrol TINGGI (Kontrol = 1) sakelar ditutup.

Gerbang transmisi bertindak seperti sakelar yang dikendalikan tegangan, dan sebagai sakelar, gerbang transmisi CMOS dapat digunakan untuk mengalihkan baik sinyal analog maupun digital yang melewati rentang tegangan penuh (dari 0V ke VDD) di kedua arah, yang seperti yang dibahas tidak mungkin dilakukan dengan satu perangkat MOS.

Kombinasi dari transistor NMOS dan PMOS bersama-sama dalam gerbang tunggal berarti bahwa transistor NMOS akan mentransfer logika yang baik "0" tetapi logika buruk "1", sedangkan transistor PMOS mentransfer logika yang baik "1" tetapi logika yang buruk "0".

Oleh karena itu, menghubungkan transistor NMOS dengan transistor PMOS secara paralel menghasilkan sakelar bilateral tunggal yang menawarkan kemampuan drive output yang efisien untuk gerbang logika CMOS yang dikendalikan oleh level logika input tunggal.