Kontrol Direct Memory Access (DMA) dalam Arsitektur Komputer

Untuk pelaksanaan program komputer, diperlukan kerja yang sinkron dari lebih dari satu komponen komputer. Misalnya, Prosesor- memberikan informasi kontrol yang diperlukan, alamat. dll, bus - untuk mentransfer informasi dan data ke dan dari memori ke perangkat I/O (Input/Output). dll. Faktor yang menarik dari sistem adalah cara menangani transfer informasi antara prosesor, memori, dan perangkat I/O (Input/Output).

Biasanya, prosesor mengontrol semua proses transfer data, langsung dari memulai transfer ke penyimpanan data di tujuan. Ini menambah beban pada prosesor dan sebagian besar waktu tetap dalam kondisi ideal, sehingga mengurangi efisiensi sistem.

Untuk mempercepat transfer data antara perangkat I/O dan memori, pengontrol DMA bertindak sebagai master stasiun. Pengontrol DMA mentransfer data dengan intervensi minimal dari prosesor.

Pengontrol DMA berisi unit alamat, untuk menghasilkan alamat dan memilih perangkat I/O untuk transfer. Ini juga berisi unit kontrol dan jumlah data untuk menjaga jumlah jumlah blok yang ditransfer dan menunjukkan arah transfer data.

Ketika transfer selesai, DMA menginformasikan prosesor dengan meningkatkan interupsi. Diagram blok khas pengontrol DMA ditunjukkan pada gambar di bawah ini.

Jika pengontrol DMA bebas, ia meminta kontrol bus dari prosesor dengan menaikkan sinyal permintaan bus. Prosesor memberikan bus ke pengontrol dengan menaikkan sinyal pemberian bus, sekarang pengontrol DMA adalah master bus.

Prosesor memulai pengontrol DMA dengan mengirimkan alamat memori, jumlah blok data yang akan ditransfer dan arah transfer data. Setelah menetapkan tugas transfer data ke pengontrol DMA, alih-alih menunggu idealnya sampai penyelesaian transfer data, prosesor melanjutkan eksekusi program setelah mengambil instruksi dari stack.

Pengontrol DMA sekarang memiliki kontrol penuh bus dan dapat berinteraksi langsung dengan memori dan perangkat I/O yang tidak tergantung pada CPU. Itu membuat transfer data sesuai dengan instruksi kontrol yang diterima oleh prosesor. Setelah selesai transfer data, ini menonaktifkan sinyal permintaan bus dan CPU menonaktifkan sinyal pemberian bus sehingga memindahkan kontrol bus ke CPU.

Ketika perangkat I/O ingin memulai transfer maka ia mengirim sinyal permintaan DMA ke pengontrol DMA, yang pengontrolnya akui jika bebas. Kemudian pengontrol meminta prosesor untuk bus, menaikkan sinyal permintaan bus. Setelah menerima sinyal bus, transfer data dari perangkat. Untuk pengontrol DMA yang disalurkan, sejumlah perangkat eksternal dapat dihubungkan.

DMA mentransfer data dalam tiga mode yang meliputi yang berikut ini.

a) Mode Burst : Dalam mode ini DMA menyerahkan bus ke CPU hanya setelah menyelesaikan seluruh transfer data. Sementara itu, jika CPU membutuhkan bus itu harus tetap ideal dan menunggu transfer data.

b) Mode Stealing Cycle : Dalam mode ini, DMA memberikan kendali bus ke CPU setelah transfer setiap byte. Itu terus mengeluarkan permintaan untuk kontrol bus, melakukan transfer satu byte dan mengembalikan bus. Dengan CPU ini tidak perlu menunggu lama jika membutuhkan bus untuk tugas dengan prioritas lebih tinggi.

c) Mode Transparan: Di sini, DMA mentransfer data hanya ketika CPU menjalankan instruksi yang tidak memerlukan penggunaan bus.

S0- Keadaan pertama, tempat pengontrol meminta bus dan menunggu pengakuan dari prosesor.

S1, S2, S3, S4 disebut keadaan kerja 8237A di mana transfer data aktual terjadi. Jika lebih banyak waktu diperlukan untuk status tunggu transfer, SW ditambahkan di antara status ini.

Untuk transfer memori-ke-memori, read-from-memory dan transfer write-to-memory harus dilakukan. Diperlukan delapan status untuk transfer tunggal. Empat keadaan bagian pertama dengan subskrip S11, S12, S13, S14 melakukan transfer baca-dari-memori dan empat S21, S22, S23, S24 berikutnya untuk transfer tulis ke memori.

DMA masuk ke kondisi ideal ketika tidak ada saluran yang meminta layanan dan melakukan status SI. SI adalah keadaan tidak aktif di mana DMA tidak aktif sampai menerima permintaan. Dalam kondisi ini, DMA berada dalam kondisi program di mana prosesor dapat memprogram DMA.

Ketika DMA berada dalam kondisi ideal dan tidak mendapatkan permintaan saluran lebih lanjut, ia mengeluarkan sinyal HRQ ke prosesor dan masuk ke status Aktif di mana ia dapat memulai transfer data baik dengan mode burst, mode stealing cycle atau mode transparan.

Urutan lebih rendah 14 bit dari nilai yang dimuat dalam register penghitungan terminal menunjukkan jumlah siklus DMA minus satu sebelum aktivasi output penghitungan Terminal. Jenis operasi untuk saluran ditunjukkan oleh dua bit paling signifikan dari register penghitungan Terminal.

Biasanya, prosesor mengontrol semua proses transfer data, langsung dari memulai transfer ke penyimpanan data di tujuan. Ini menambah beban pada prosesor dan sebagian besar waktu tetap dalam kondisi ideal, sehingga mengurangi efisiensi sistem.

Untuk mempercepat transfer data antara perangkat I/O dan memori, pengontrol DMA bertindak sebagai master stasiun. Pengontrol DMA mentransfer data dengan intervensi minimal dari prosesor.

Apa itu Pengendali DMA?

Istilah DMA singkatan dari Direct Memory Access atau akses memori langsung. Perangkat perangkat keras yang digunakan untuk akses memori langsung disebut pengontrol DMA. Pengontrol DMA adalah unit kontrol, bagian dari rangkaian antarmuka perangkat I/O, yang dapat mentransfer blok data antara perangkat I/O dan memori utama dengan intervensi minimal dari prosesor.Diagram Pengontrol DMA dalam Arsitektur Komputer

Pengontrol DMA menyediakan antarmuka antara bus dan perangkat input-output. Meskipun mentransfer data tanpa campur tangan prosesor, ia dikendalikan oleh prosesor. Prosesor memulai pengontrol DMA dengan mengirim alamat awal, jumlah kata dalam blok data dan arah transfer data. Yaitu dari perangkat I/O ke memori atau dari memori utama ke perangkat I/O. Lebih dari satu perangkat eksternal dapat dihubungkan ke pengontrol DMA.

Pengontrol DMA berisi unit alamat, untuk menghasilkan alamat dan memilih perangkat I/O untuk transfer. Ini juga berisi unit kontrol dan jumlah data untuk menjaga jumlah jumlah blok yang ditransfer dan menunjukkan arah transfer data.

Ketika transfer selesai, DMA menginformasikan prosesor dengan meningkatkan interupsi. Diagram blok khas pengontrol DMA ditunjukkan pada gambar di bawah ini.

Prinsip Kerja DMA Controller

Pengontrol DMA harus berbagi bus dengan prosesor untuk melakukan transfer data. Perangkat yang memegang bus pada waktu tertentu disebut bus master. Ketika transfer dari perangkat I/O ke memori atau sebaliknya harus dilakukan, prosesor menghentikan eksekusi arus program, menambah penghitung program, memindahkan data di atas tumpukan, kemudian mengirim sinyal pilih DMA ke pengontrol DMA ke alamat bus.Jika pengontrol DMA bebas, ia meminta kontrol bus dari prosesor dengan menaikkan sinyal permintaan bus. Prosesor memberikan bus ke pengontrol dengan menaikkan sinyal pemberian bus, sekarang pengontrol DMA adalah master bus.

Prosesor memulai pengontrol DMA dengan mengirimkan alamat memori, jumlah blok data yang akan ditransfer dan arah transfer data. Setelah menetapkan tugas transfer data ke pengontrol DMA, alih-alih menunggu idealnya sampai penyelesaian transfer data, prosesor melanjutkan eksekusi program setelah mengambil instruksi dari stack.

Pengontrol DMA sekarang memiliki kontrol penuh bus dan dapat berinteraksi langsung dengan memori dan perangkat I/O yang tidak tergantung pada CPU. Itu membuat transfer data sesuai dengan instruksi kontrol yang diterima oleh prosesor. Setelah selesai transfer data, ini menonaktifkan sinyal permintaan bus dan CPU menonaktifkan sinyal pemberian bus sehingga memindahkan kontrol bus ke CPU.

Ketika perangkat I/O ingin memulai transfer maka ia mengirim sinyal permintaan DMA ke pengontrol DMA, yang pengontrolnya akui jika bebas. Kemudian pengontrol meminta prosesor untuk bus, menaikkan sinyal permintaan bus. Setelah menerima sinyal bus, transfer data dari perangkat. Untuk pengontrol DMA yang disalurkan, sejumlah perangkat eksternal dapat dihubungkan.

DMA mentransfer data dalam tiga mode yang meliputi yang berikut ini.

a) Mode Burst : Dalam mode ini DMA menyerahkan bus ke CPU hanya setelah menyelesaikan seluruh transfer data. Sementara itu, jika CPU membutuhkan bus itu harus tetap ideal dan menunggu transfer data.

b) Mode Stealing Cycle : Dalam mode ini, DMA memberikan kendali bus ke CPU setelah transfer setiap byte. Itu terus mengeluarkan permintaan untuk kontrol bus, melakukan transfer satu byte dan mengembalikan bus. Dengan CPU ini tidak perlu menunggu lama jika membutuhkan bus untuk tugas dengan prioritas lebih tinggi.

c) Mode Transparan: Di sini, DMA mentransfer data hanya ketika CPU menjalankan instruksi yang tidak memerlukan penggunaan bus.

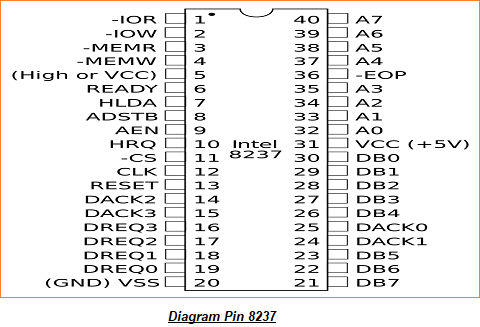

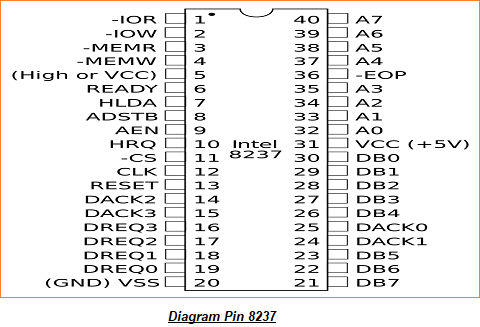

8237 Pengendali DMA

- 8237 memiliki 4 saluran I/O bersama dengan fleksibilitas meningkatkan jumlah saluran.

- Setiap saluran dapat diprogram secara individual dan memiliki alamat 64k dan kemampuan data.

- Blok kontrol timing, blok kontrol perintah Program, Blok Encoder Prioritas adalah tiga blok utama 8237A.

- Sinyal pengaturan waktu internal dan eksternal digerakkan oleh blok kontrol pengaturan waktu.

- Berbagai perintah yang diberikan oleh mikroprosesor ke DMA didekodekan oleh blok kontrol perintah program.

- Saluran mana yang harus diberi prioritas tertinggi ditentukan oleh blok pembuat enkode prioritas.

- 8237A memiliki 27 register internal.

S0- Keadaan pertama, tempat pengontrol meminta bus dan menunggu pengakuan dari prosesor.

S1, S2, S3, S4 disebut keadaan kerja 8237A di mana transfer data aktual terjadi. Jika lebih banyak waktu diperlukan untuk status tunggu transfer, SW ditambahkan di antara status ini.

Untuk transfer memori-ke-memori, read-from-memory dan transfer write-to-memory harus dilakukan. Diperlukan delapan status untuk transfer tunggal. Empat keadaan bagian pertama dengan subskrip S11, S12, S13, S14 melakukan transfer baca-dari-memori dan empat S21, S22, S23, S24 berikutnya untuk transfer tulis ke memori.

DMA masuk ke kondisi ideal ketika tidak ada saluran yang meminta layanan dan melakukan status SI. SI adalah keadaan tidak aktif di mana DMA tidak aktif sampai menerima permintaan. Dalam kondisi ini, DMA berada dalam kondisi program di mana prosesor dapat memprogram DMA.

Ketika DMA berada dalam kondisi ideal dan tidak mendapatkan permintaan saluran lebih lanjut, ia mengeluarkan sinyal HRQ ke prosesor dan masuk ke status Aktif di mana ia dapat memulai transfer data baik dengan mode burst, mode stealing cycle atau mode transparan.

8257 Pengendali DMA

Ketika dipasangkan dengan single Intel 8212 I/O port perangkat, 8257 bentuk DMA controller lengkap 4 channel DMA controller. Setelah menerima permintaan transfer, controller 8257-- Mengakuisisi kontrol atas bus sistem dari prosesor.

- Perangkat yang terhubung ke saluran prioritas tertinggi diakui.

- Bit-bit paling tidak signifikan dari alamat memori dipindahkan ke baris alamat A0-A7 dari bus sistem.

- 8 bit paling signifikan dari alamat memori didorong ke 8212 I/O port melalui jalur data.

- Menghasilkan sinyal kontrol yang sesuai untuk transfer data antara periferal dan lokasi memori yang dialamatkan.

- Ketika jumlah byte yang ditentukan ditransfer, controller menginformasikan akhir transfer CPU dengan mengaktifkan output terminal count (TC).

Urutan lebih rendah 14 bit dari nilai yang dimuat dalam register penghitungan terminal menunjukkan jumlah siklus DMA minus satu sebelum aktivasi output penghitungan Terminal. Jenis operasi untuk saluran ditunjukkan oleh dua bit paling signifikan dari register penghitungan Terminal.

Kelebihan dan Kekurangan Kontroler DMA

Kelebihan dan kekurangan dari pengontrol DMA meliputi yang berikut ini.Kelebihan

- DMA mempercepat operasi memori dengan mem-bypass keterlibatan CPU.

- Overload kerja pada CPU berkurang.

- Untuk setiap transfer, hanya beberapa siklus jam yang diperlukan

Kekurangan

- Masalah koherensi cache dapat dilihat ketika DMA digunakan untuk transfer data.

- Meningkatkan harga sistem.